3–28 Chapter 3: Cyclone IV Dynamic Reconfiguration

Dynamic Reconfiguration Modes

Cyclone IV Device Handbook, November 2011 Altera Corporation

Volume 2

Clocking/Interface Options

The following describes the Clocking/Interface options available in Cyclone IV GX

devices. The core clocking setup describes the transceiver core clocks that are the

write and read clocks of the Transmit Phase Compensation FIFO and the Receive

Phase Compensation FIFO, respectively. Core clocking is classified as transmitter core

clocking and receiver core clocking.

Table 3–6 lists the supported clocking interface settings for channel reconfiguration

mode in Cyclone IV GX devices.

Transmitter core clocking refers to the clock that is used to write the parallel data from

the FPGA fabric into the Transmit Phase Compensation FIFO. You can use one of the

following clocks to write into the Transmit Phase Compensation FIFO:

■

tx_coreclk

—you can use a clock of the same frequency as

tx_clkout

from the

FPGA fabric to provide the write clock to the Transmit Phase Compensation FIFO.

If you use

tx_coreclk

, it overrides the

tx_clkout

options in the ALTGX

MegaWizard Plug-In Manager.

■

tx_clkout

—the Quartus II software automatically routes

tx_clkout

to the FPGA

fabric and back into the Transmit Phase Compensation FIFO.

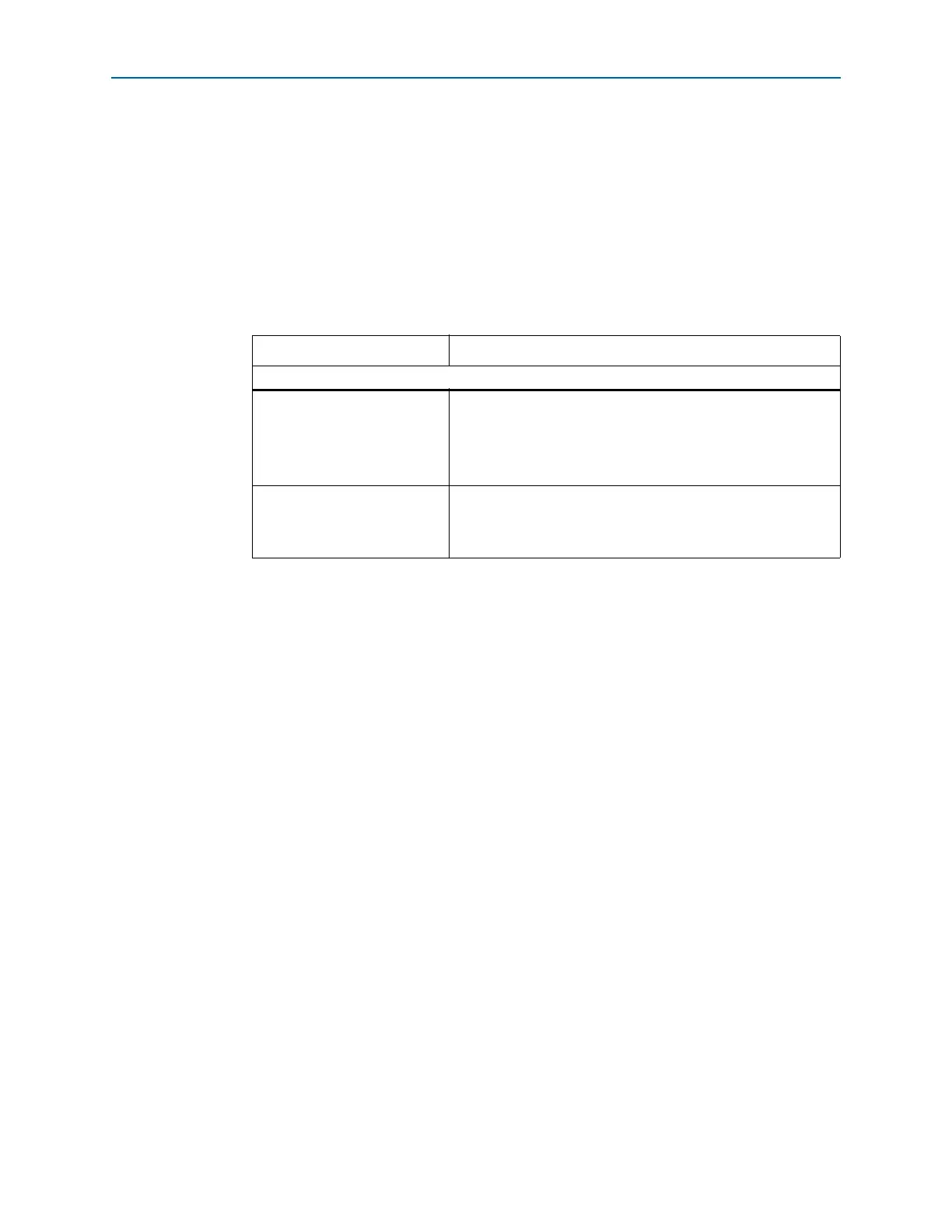

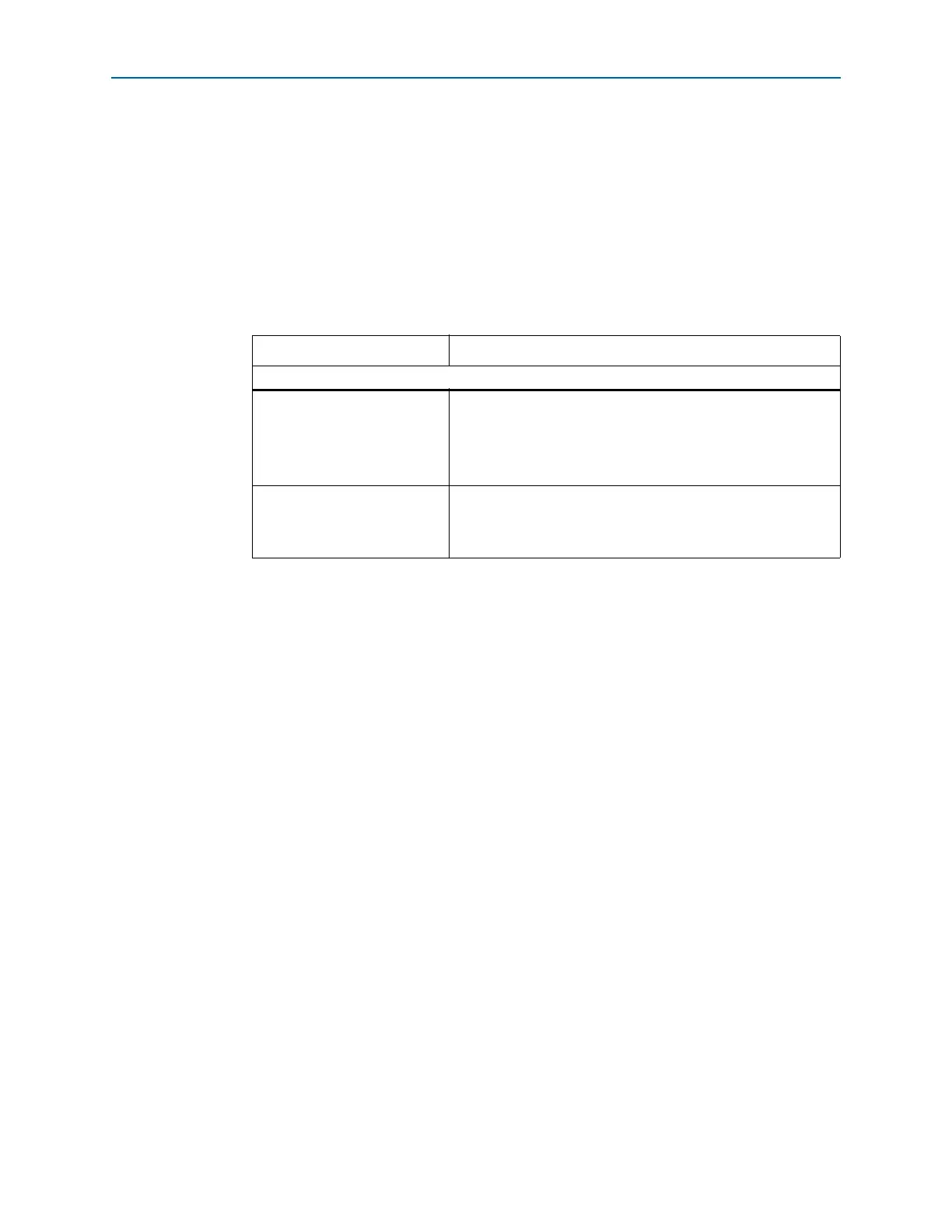

Table 3–6. Dynamic Reconfiguration Clocking Interface Settings in Channel Reconfiguration

Mode

ALTGX Setting Description

Dynamic Reconfiguration Channel Internal and Interface Settings

How should the receivers be

clocked?

Select one of the available options:

■ Share a single transmitter core clock between receivers

■ Use the respective channel transmitter core clocks

■ Use the respective channel receiver core clocks

How should the transmitters be

clocked?

Select one of the available options:

■ Share a single transmitter core clock between transmitters

■ Use the respective channel transmitter core clocks

Loading...

Loading...