Chapter 3: Cyclone IV Dynamic Reconfiguration 3–29

Dynamic Reconfiguration Modes

November 2011 Altera Corporation Cyclone IV Device Handbook,

Volume 2

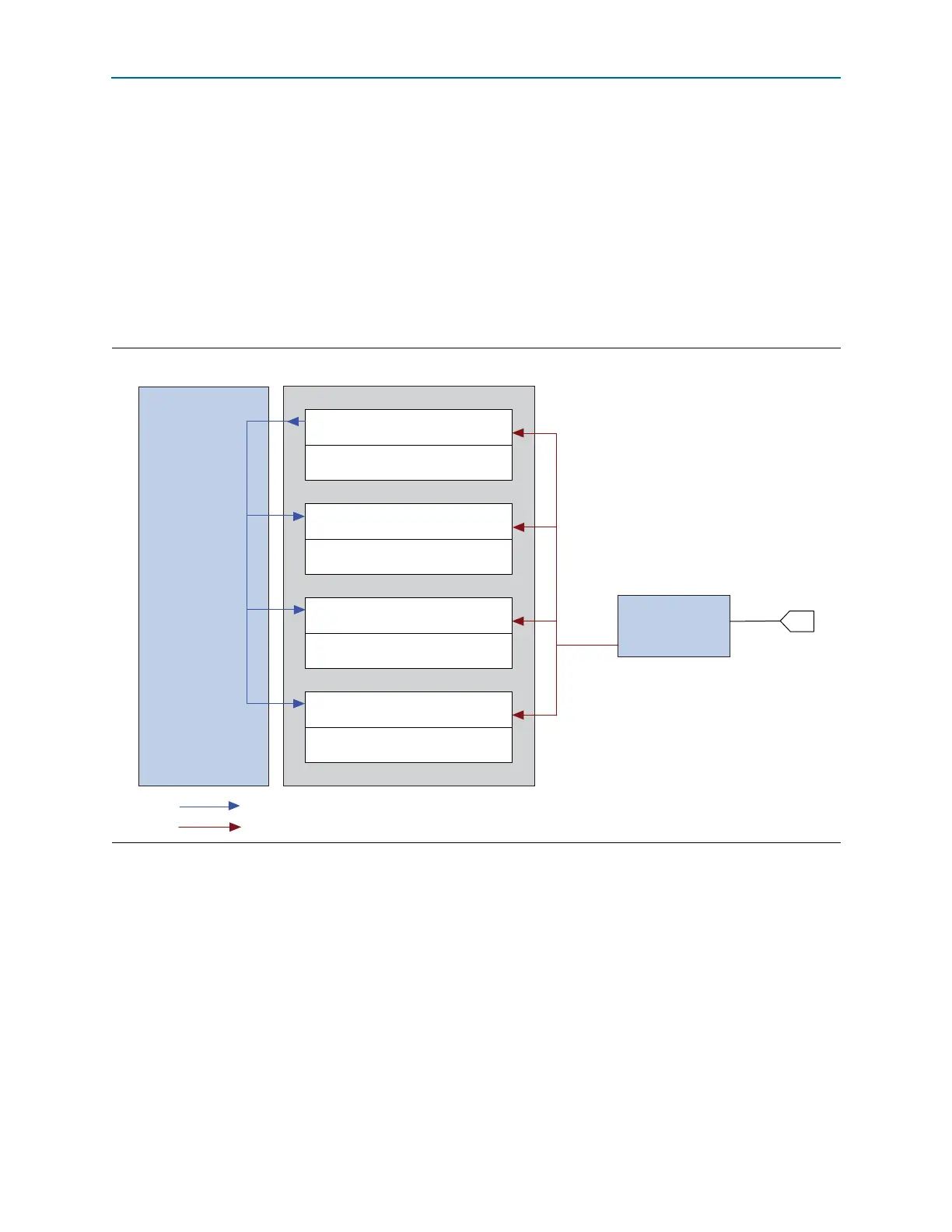

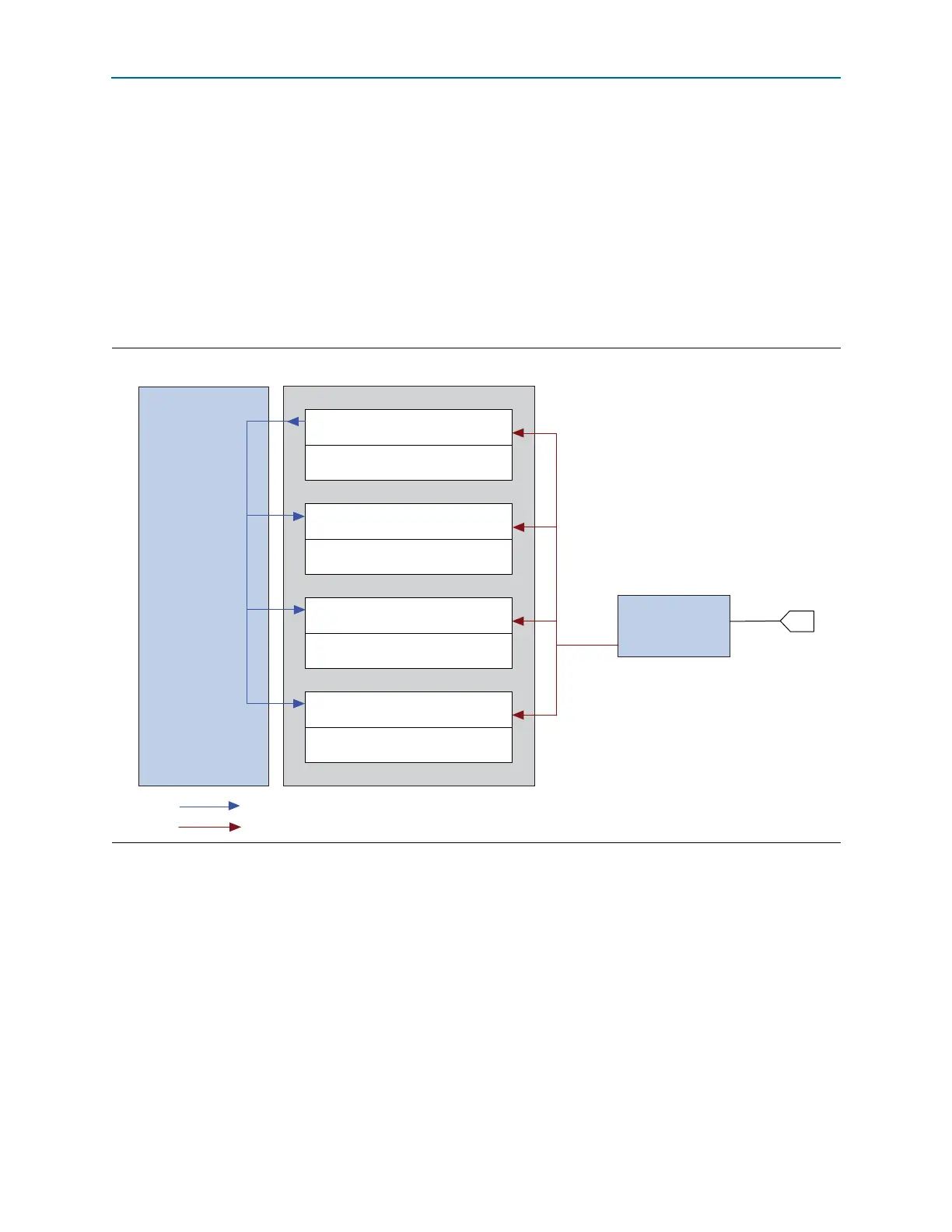

Option 1: Share a Single Transmitter Core Clock Between Transmitters

■ Enable this option if you want

tx_clkout

of the first channel (channel 0) of the

transceiver block to provide the write clock to the Transmitter Phase

Compensation FIFOs of the remaining channels in the transceiver block.

■ This option is typically enabled when all the channels of a transceiver block have

the same functional mode and data rate and are reconfigured to the identical

functional mode and data rate.

Figure 3–11 shows the sharing of channel 0’s

tx_clkout

between all four regular

channels of a transceiver block.

Figure 3–11. Option 1 for Transmitter Core Clocking (Channel Reconfiguration Mode)

TX0

TX1

TX2

TX3

RX3

RX2

RX1

RX0

MPLL

FPGA Fabric

Transceiver Block

tx_clkout[0]

Low-speed parallel clock (tx_clkout0)

High-speed serial clock generated by the MPLL

Loading...

Loading...