Chapter 1: Cyclone IV Transceivers Architecture 1–3

Transceiver Architecture

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

For more information about the transceiver architecture, refer to the following

sections:

■ “Architectural Overview” on page 1–4

■ “Transmitter Channel Datapath” on page 1–5

■ “Receiver Channel Datapath” on page 1–11

■ “Transceiver Clocking Architecture” on page 1–26

■ “Transceiver Channel Datapath Clocking” on page 1–29

■ “FPGA Fabric-Transceiver Interface Clocking” on page 1–43

■ “Calibration Block” on page 1–45

■ “PCI-Express Hard IP Block” on page 1–46

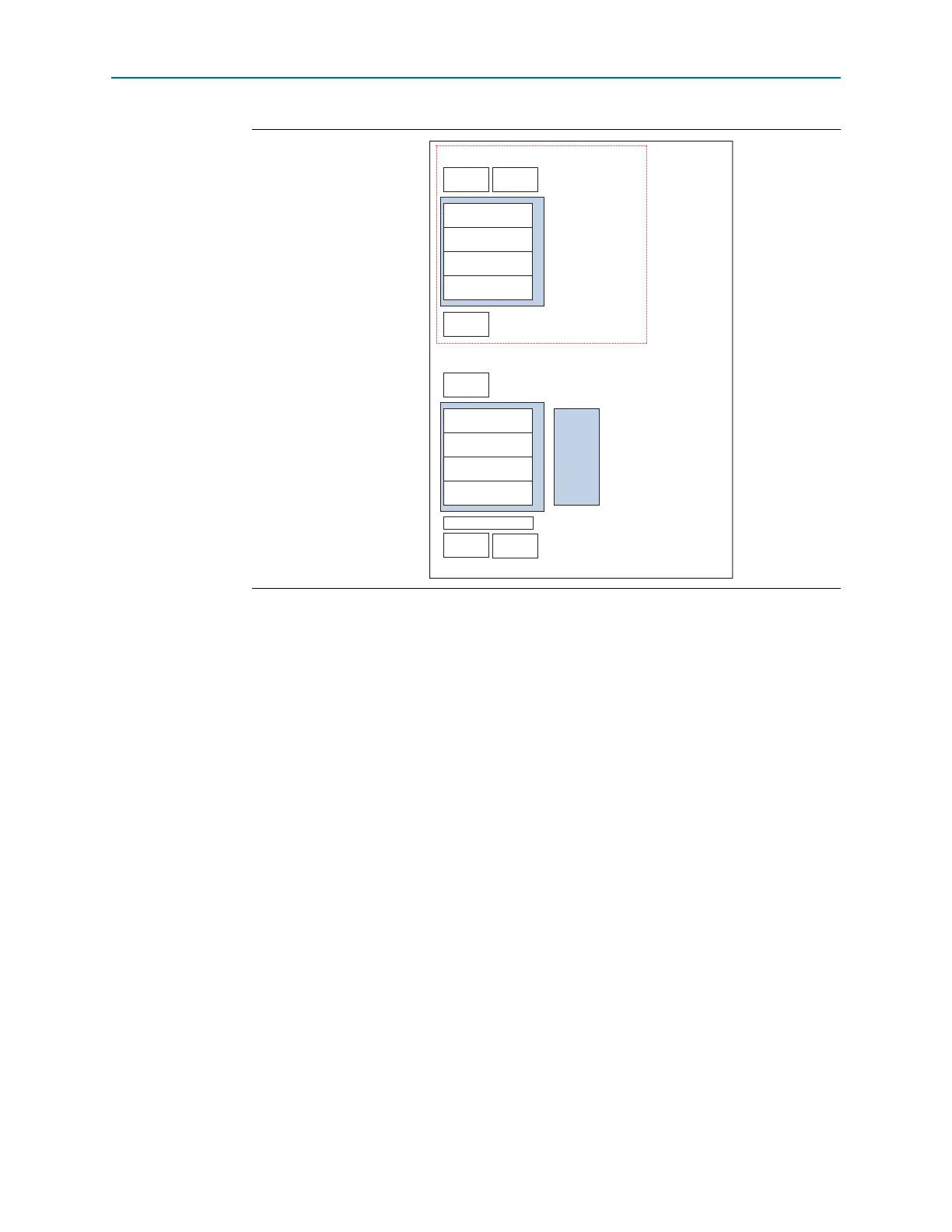

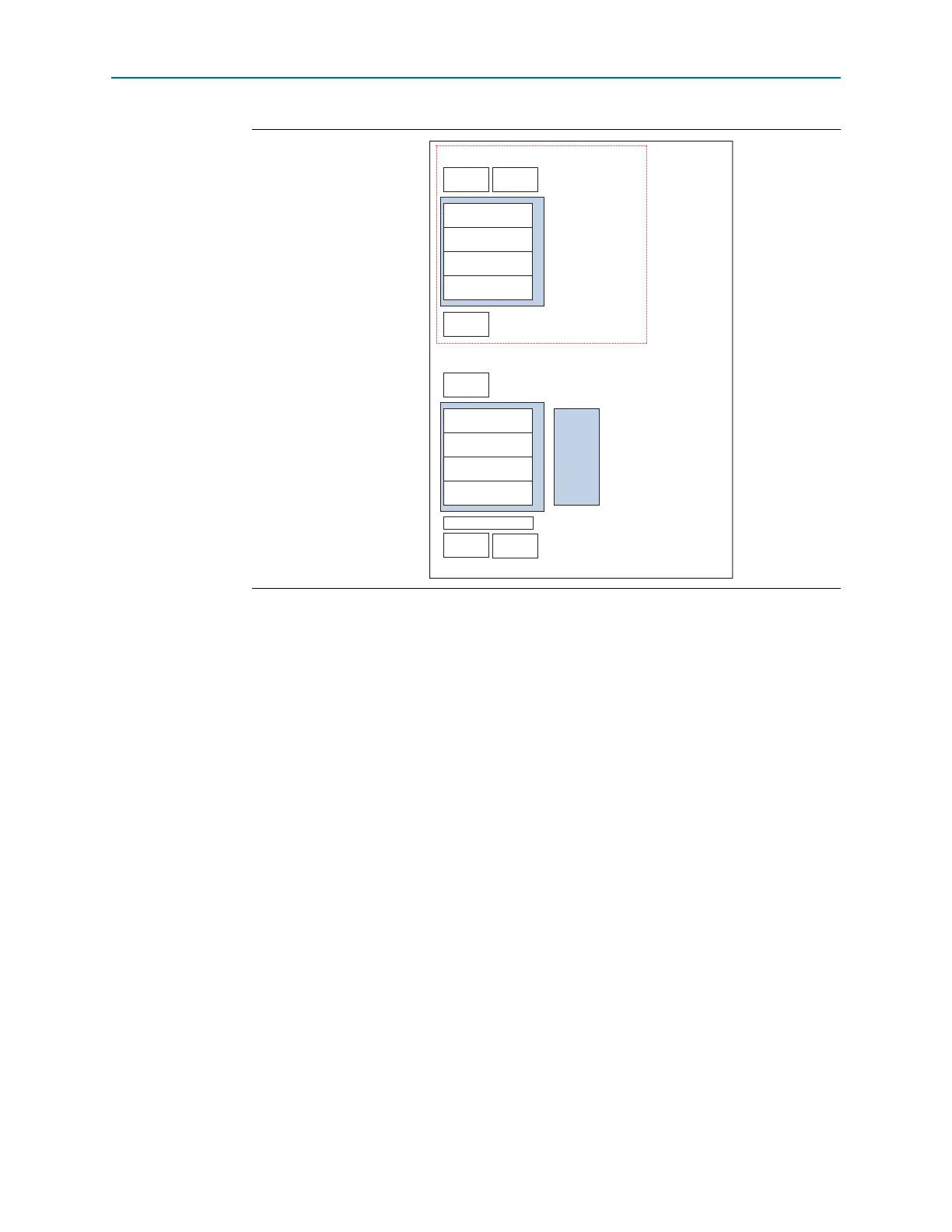

Figure 1–2. F484 and Larger Packages with Transceiver Channels for Cyclone IV GX Devices

MPLL_8 GPLL_2

MPLL_7

Channel 3

Channel 2

F484 and larger

packages

Channel 1

Channel 0

MPLL_6

Not applicable in

F484 package

MPLL_5

Calibration Block

Channel 3

Channel 2

GPLL_1

PCIe

hard IP

Channel 1

Channel 0

Transceiver

Block GXBL0

Transceiver

Block GXBL1

Loading...

Loading...