1–2 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Architecture

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

1 The Cyclone IV GX device includes a hard intellectual property (IP) implementation

of the PCIe MegaCore

®

functions, supporting Gen1 ×1, ×2, and ×4 initial lane widths

configured in the root port or endpoint mode. For more information, refer to “PCI-

Express Hard IP Block” on page 1–46.

Transceiver Architecture

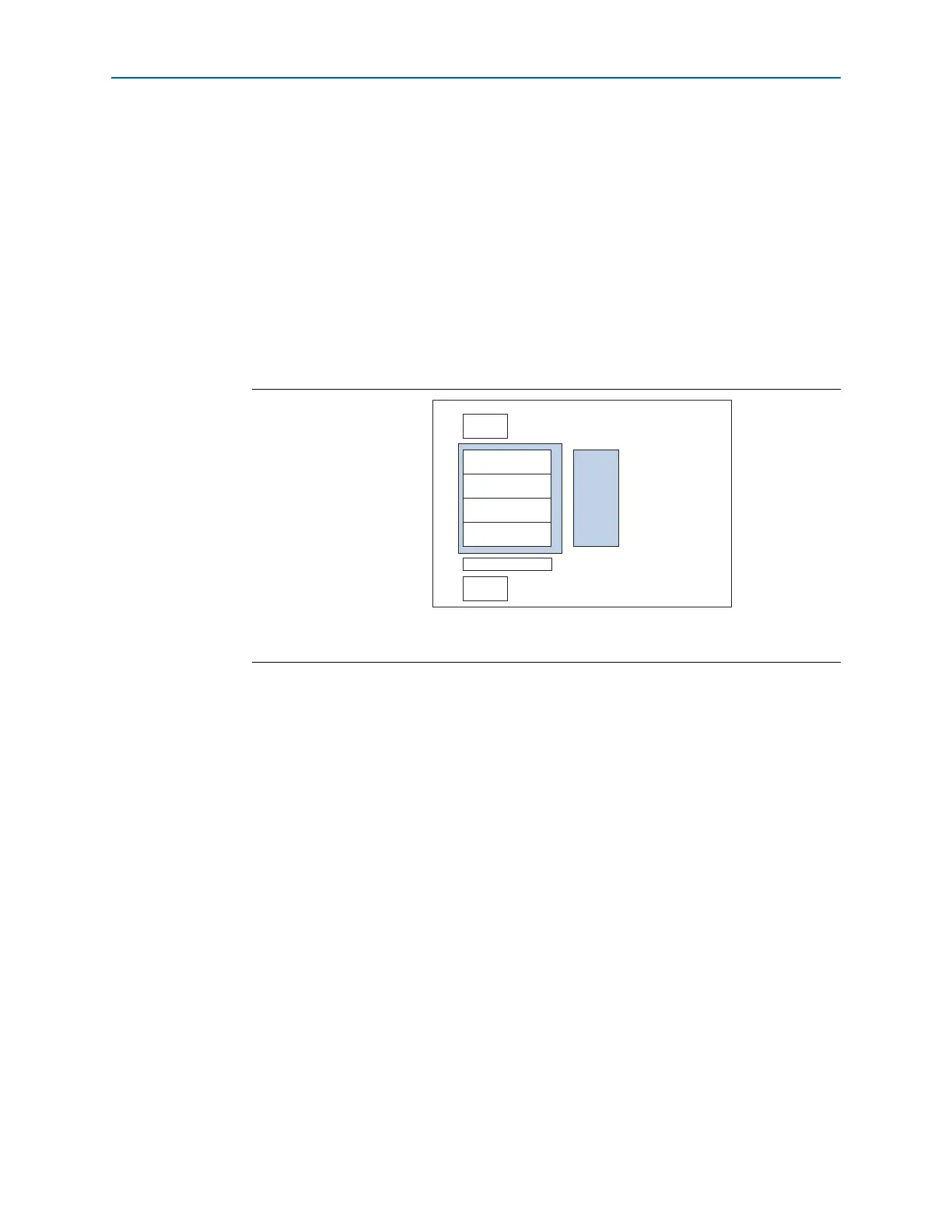

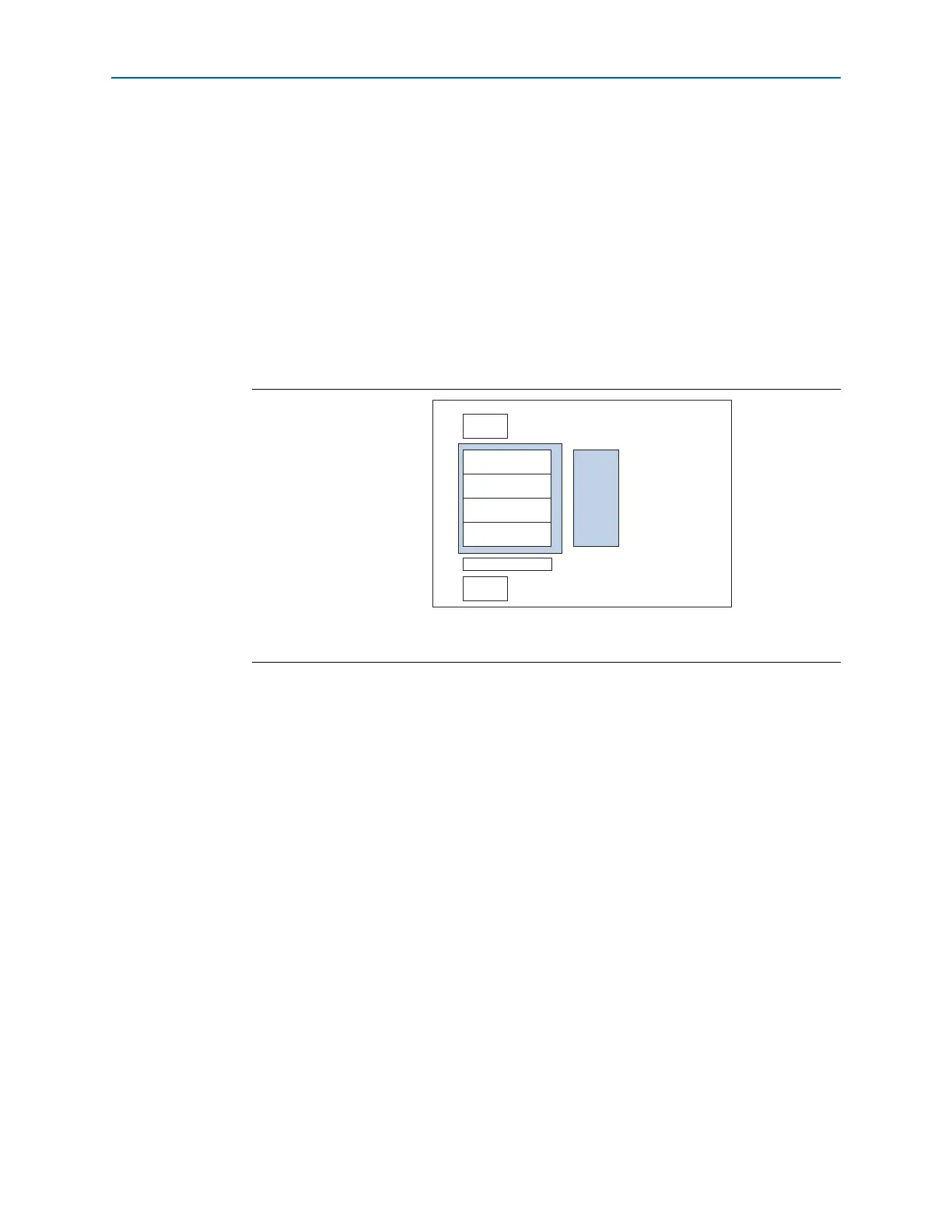

Cyclone IV GX devices offer either one or two transceiver blocks per device,

depending on the package. Each block consists of four full-duplex (transmitter and

receiver) channels, located on the left side of the device (in a die-top view). Figure 1–1

and Figure 1–2 show the die-top view of the transceiver block and related resource

locations in Cyclone IV GX devices.

Figure 1–1. F324 and Smaller Packages with Transceiver Channels for Cyclone IV GX Devices

Note to Figure 1–1:

(1) Channel 2 and Channel 3 are not available in the F169 and smaller packages.

MPLL_2

MPLL_1

Channel 3 (1)

Channel 2 (1)

PCIe

hard IP

F324 and smaller

packages

Channel 1

Channel 0

Transceiver

Block GXBL0

Calibration Block

Loading...

Loading...