Chapter 1: Cyclone IV Device Datasheet 1–17

Switching Characteristics

December 2016 Altera Corporation Cyclone IV Device Handbook,

Volume 3

Transceiver Performance Specifications

Table 1–21 lists the Cyclone IV GX transceiver specifications.

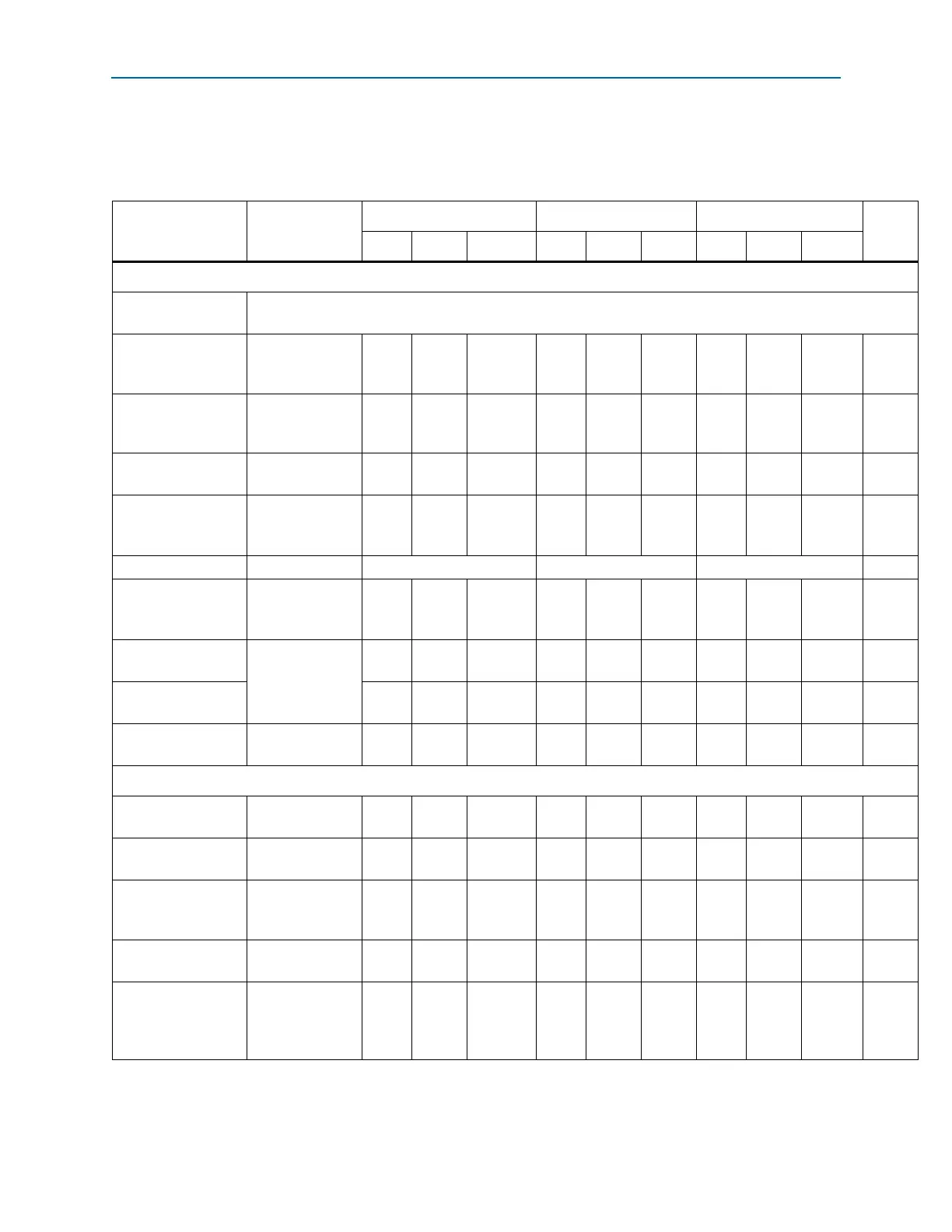

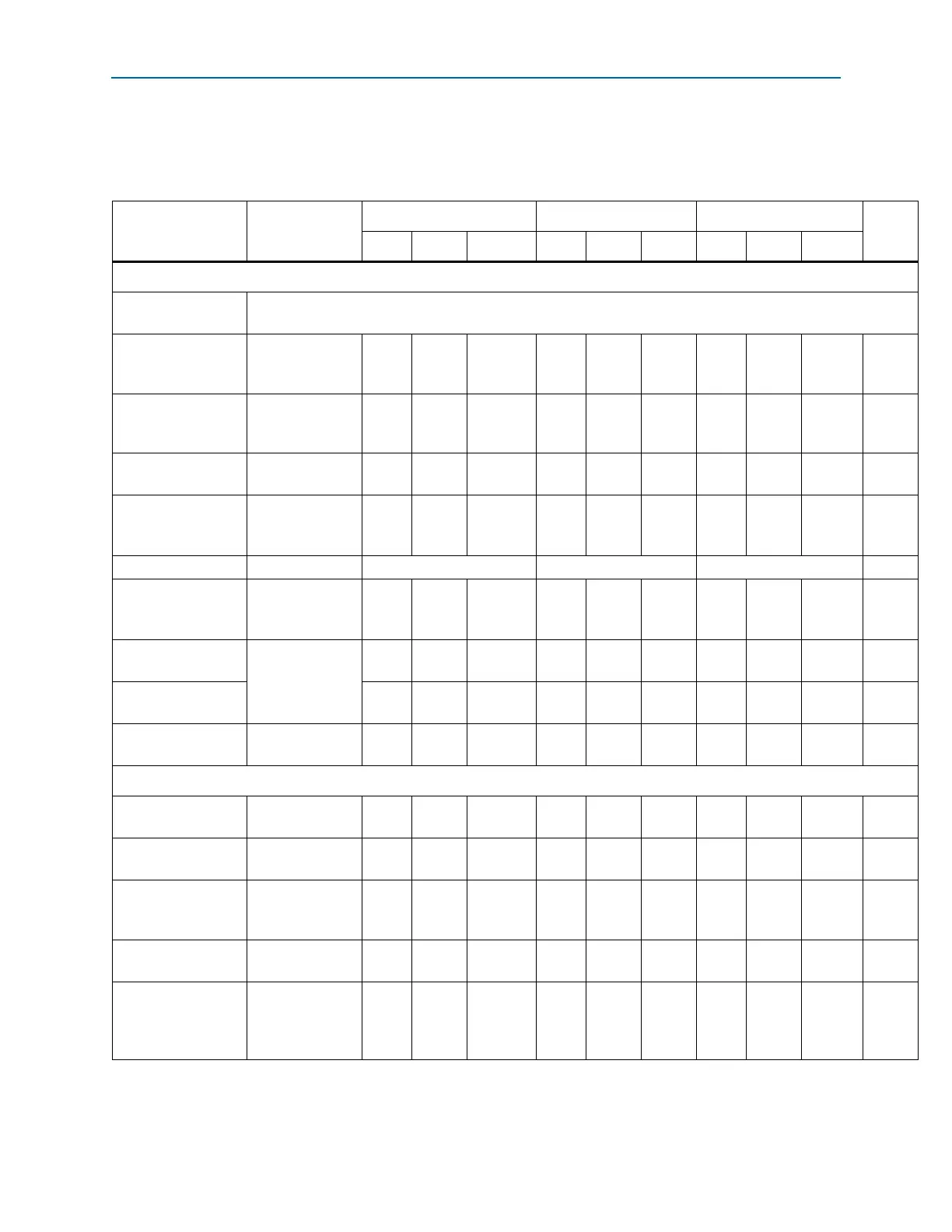

Table 1–21. Transceiver Specification for Cyclone IV GX Devices (Part 1 of 4)

Symbol/

Description

Conditions

C6 C7, I7 C8

Unit

Min Typ Max Min Typ Max Min Typ Max

Reference Clock

Supported I/O

Standards

1.2 V PCML, 1.5 V PCML, 3.3 V PCML, Differential LVPECL, LVDS, HCSL

Input frequency

from

REFCLK

input

pins

— 50 — 156.25 50 — 156.25 50 — 156.25 MHz

Spread-spectrum

modulating clock

frequency

Physical interface

for PCI Express

(PIPE) mode

30 — 33 30 — 33 30 — 33 kHz

Spread-spectrum

downspread

PIPE mode —

0 to

–0.5%

——

0 to

–0.5%

——

0 to

–0.5%

——

Peak-to-peak

differential input

voltage

— 0.1 — 1.6 0.1 — 1.6 0.1 — 1.6 V

V

ICM

(AC coupled) — 1100 ± 5% 1100 ± 5% 1100 ± 5% mV

V

ICM

(DC coupled)

HCSL I/O

standard for PCIe

reference clock

250 — 550 250 — 550 250 — 550 mV

Transmitter REFCLK

Phase Noise

(1)

Frequency offset

= 1MHz – 8MHZ

——

–123 — — –123 — — –123 dBc/Hz

Transmitter REFCLK

Total Jitter

(1)

— — 42.3 — — 42.3 — — 42.3 ps

R

ref

——

2000

± 1%

——

2000

± 1%

——

2000

± 1%

—

Transceiver Clock

cal_blk_clk

clock

frequency

— 10 — 125 10 — 125 10 — 125 MHz

fixedclk

clock

frequency

PCIe Receiver

Detect

— 125 — — 125 — — 125 — MHz

reconfig_clk

clock frequency

Dynamic

reconfiguration

clock frequency

2.5/

37.5

(2)

—50

2.5/

37.5

(2)

—50

2.5/

37.5

(2)

—50MHz

Delta time between

reconfig_clk

———2——2——2ms

Transceiver block

minimum

power-down pulse

width

——1——1——1—µs

Loading...

Loading...