1–20 Chapter 1: Cyclone IV Device Datasheet

Switching Characteristics

Cyclone IV Device Handbook, December 2016 Altera Corporation

Volume 3

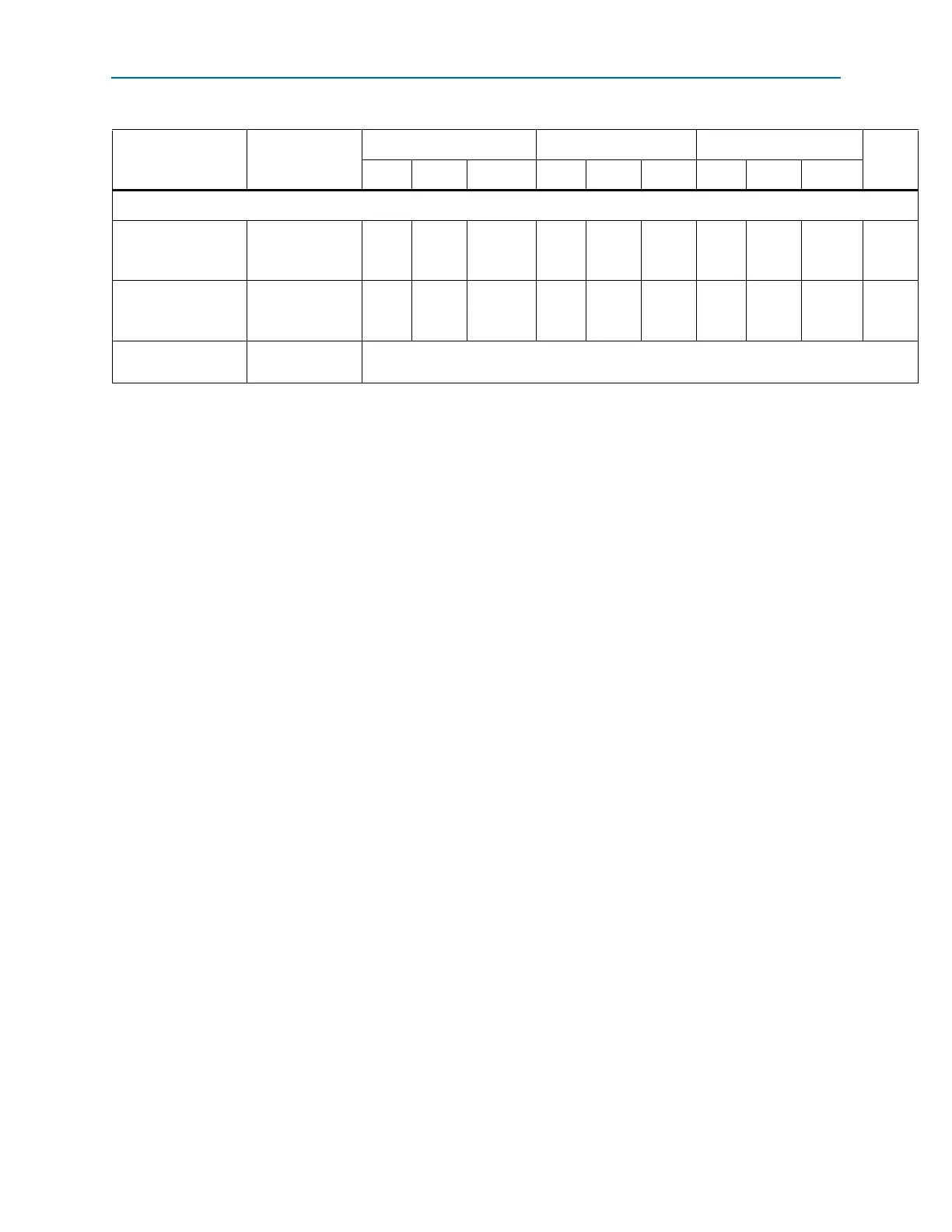

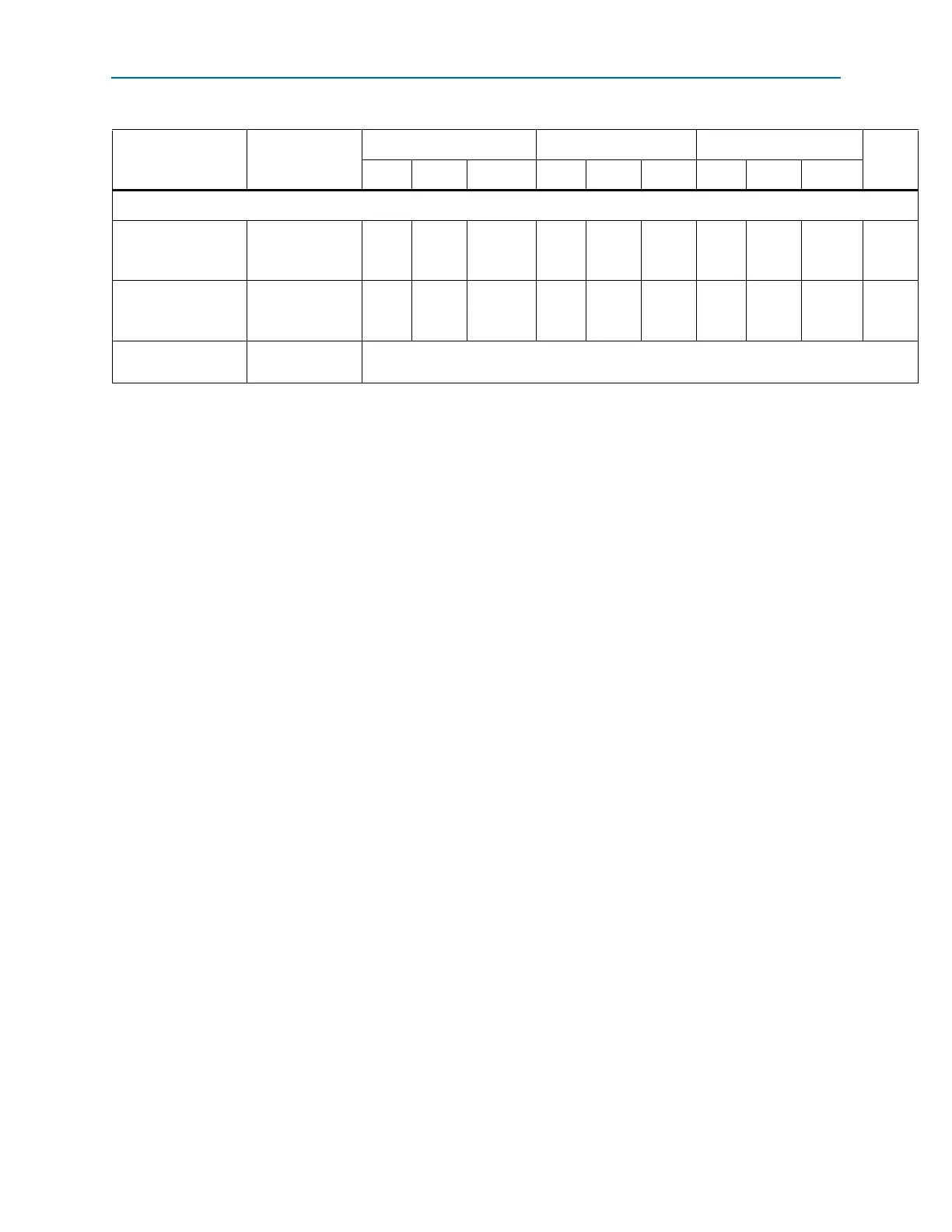

PLD-Transceiver Interface

Interface speed

(F324 and smaller

package)

— 25 — 125 25 — 125 25 — 125 MHz

Interface speed

(F484 and larger

package)

— 25 — 156.25 25 — 156.25 25 — 156.25 MHz

Digital reset pulse

width

— Minimum is 2 parallel clock cycles

Notes to Table 1–21:

(1) This specification is valid for transmitter output jitter specification with a maximum total jitter value of 112 ps, typically for 3.125 Gbps SRIO and XAUI

protocols.

(2) The minimum

reconfig_clk

frequency is 2.5 MHz if the transceiver channel is configured in Transmitter Only mode. The minimum

reconfig_clk

frequency

is 37.5 MHz if the transceiver channel is configured in Receiver Only or Receiver and Transmitter mode.

(3) The device cannot tolerate prolonged operation at this absolute maximum.

(4) The rate matcher supports only up to ±300 parts per million (ppm).

(5) Supported for the F169 and F324 device packages only.

(6) Supported for the F484, F672, and F896 device packages only. Pending device characterization.

(7) To support CDR ppm tolerance greater than ±300 ppm, implement ppm detector in user logic and configure CDR to Manual Lock Mode.

(8) Asynchronous spread-spectrum clocking is not supported.

(9) For the EP4CGX30 (F484 package only), EP4CGX50, and EP4CGX75 devices, the CDR ppl tolerance is ±200 ppm.

(10) Time taken until

pll_locked

goes high after

pll_powerdown

deasserts.

(11) Time that the CDR must be kept in lock-to-reference mode after

rx_analogreset

deasserts and before

rx_locktodata

is asserted in manual mode.

(12) Time taken to recover valid data after the

rx_locktodata

signal is asserted in manual mode (Figure 1–2), or after

rx_freqlocked

signal goes high in

automatic mode (Figure 1–3).

(13) Time taken to recover valid data after the

rx_locktodata

signal is asserted in manual mode.

(14) Time taken to recover valid data after the

rx_freqlocked

signal goes high in automatic mode.

(15) To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

Table 1–21. Transceiver Specification for Cyclone IV GX Devices (Part 4 of 4)

Symbol/

Description

Conditions

C6 C7, I7 C8

Unit

Min Typ Max Min Typ Max Min Typ Max

Loading...

Loading...