1–66 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Functional Modes

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

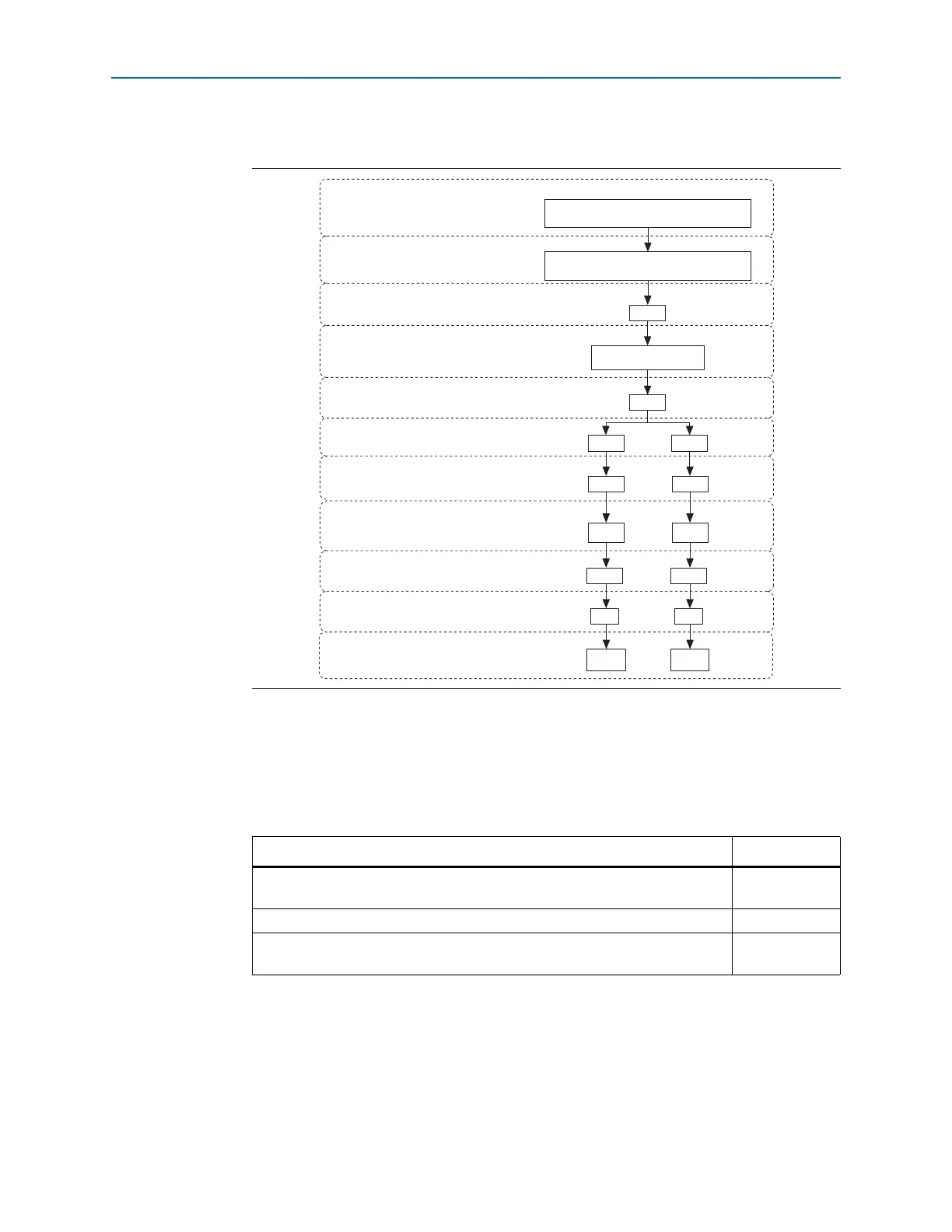

Figure 1–61 shows the transceiver configuration in Serial RapidIO mode.

Lane Synchronization

In Serial RapidIO mode, the word aligner is compliant to the SRIO Specification 1.3

and is configured in automatic synchronization state machine mode with the

parameter settings as listed in Table 1–20.

Figure 1–61. Transceiver Configuration in Serial RapidIO Mode

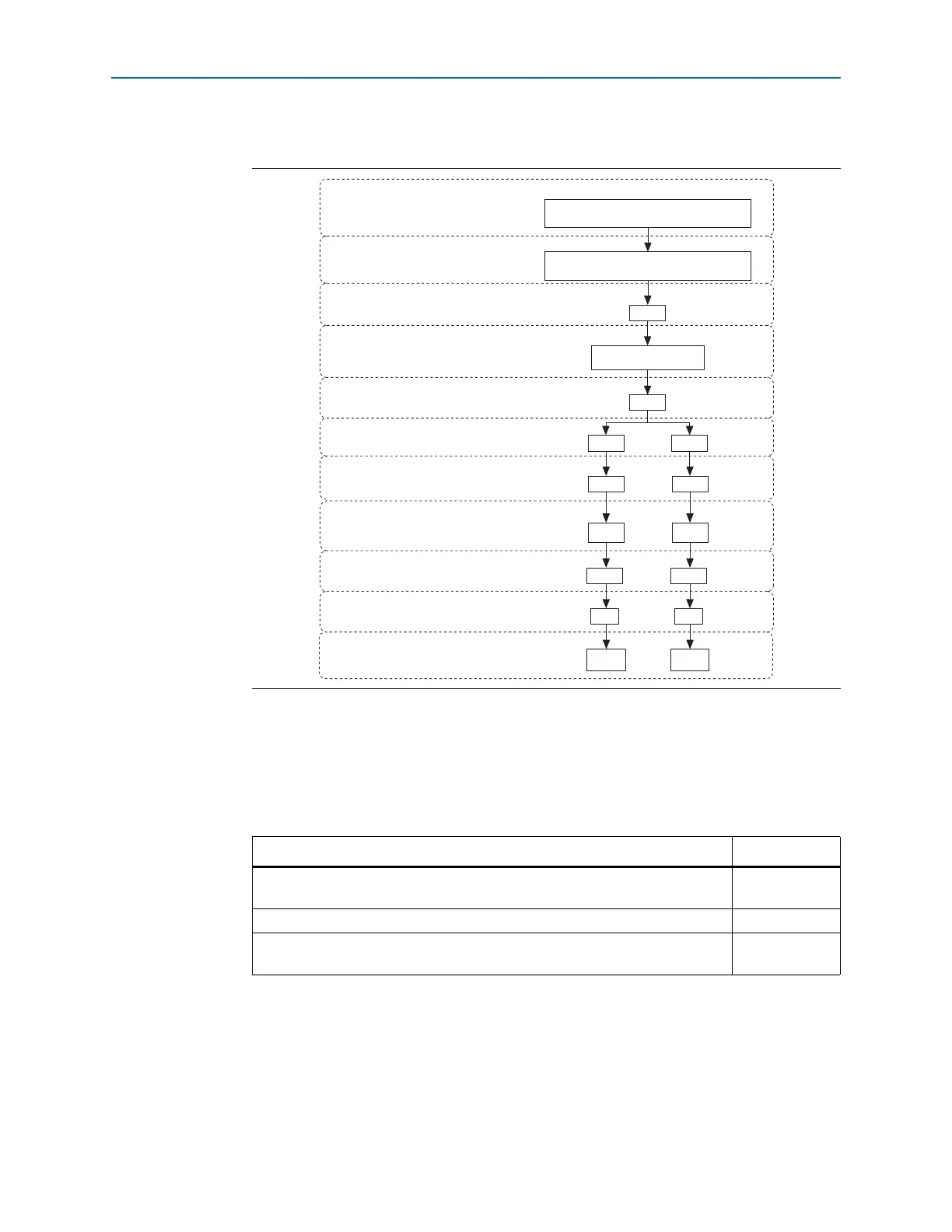

Table 1–20. Synchronization State Machine Parameters

(1)

Parameter Value

Number of valid synchronization (/K28.5/) code groups received to achieve

synchronization

127

Number of erroneous code groups received to lose synchronization 3

Number of continuous good code groups received to reduce the error count by

one

255

Note to Table 1–20:

(1) The word aligner supports 10-bit pattern lengths in SRIO mode.

Functional Mode

Channel Bonding

Low-Latency PCS

Word Aligner (Pattern Length)

8B/10B Encoder/Decoder

Rate Match FIFO

Byte SERDES

Byte Ordering

FPGA Fabric-to-Transceiver

Interface Width

FPGA Fabric-to-Transceiver

Interface Frequency (MHz)

Disabled

Automatic Synchronization

State Machine (10-Bit)

SRIO

×1

Data Rate (Gbps)

Disabled

Disabled

1.25/2.5/

3.125

1.25/2.5/

3.125

16-Bit

Disabled

Enabled

Enabled Enabled

Enabled

62.5/125/

156.25

16-Bit

62.5/125/

156.25

Loading...

Loading...