Chapter 1: Cyclone IV Transceivers Architecture 1–65

Transceiver Functional Modes

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

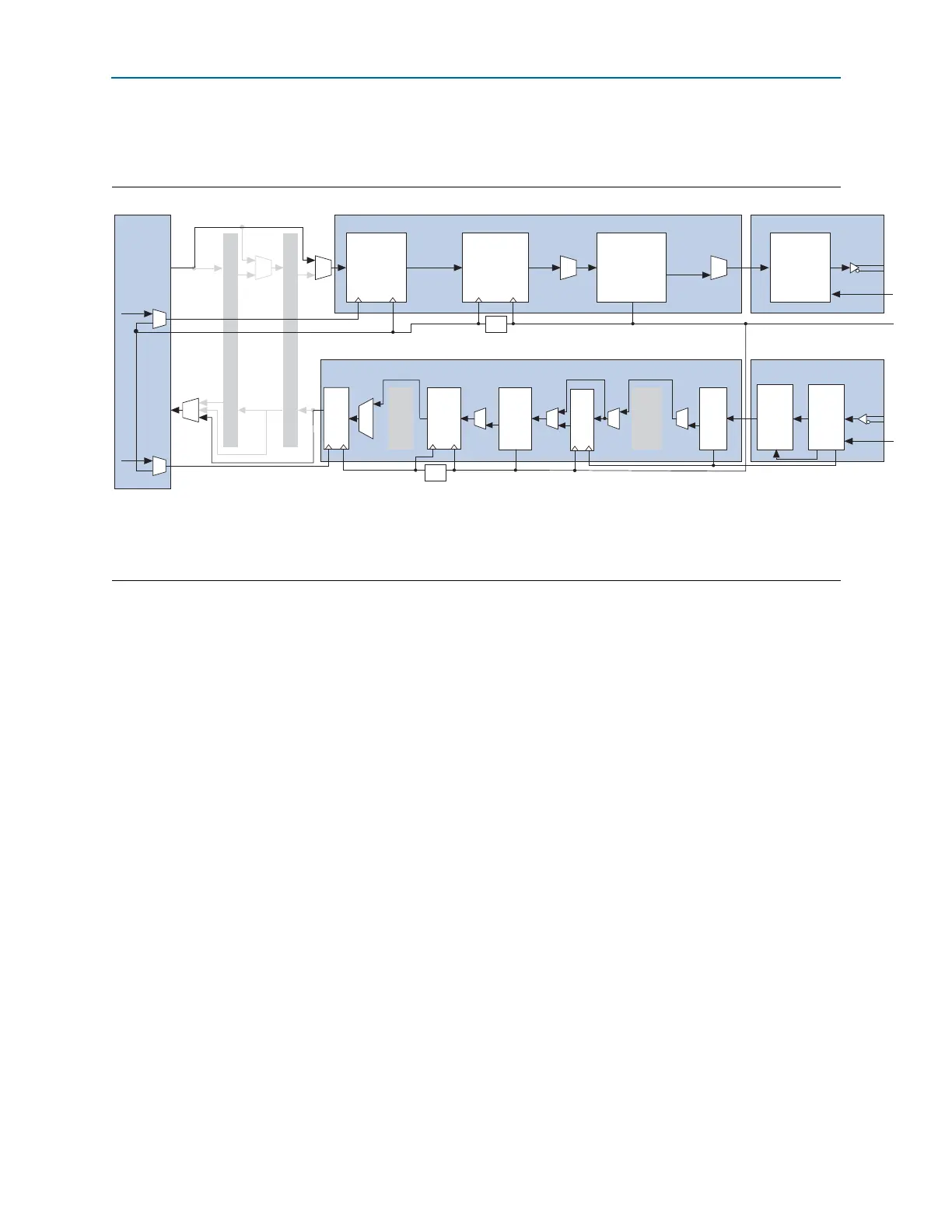

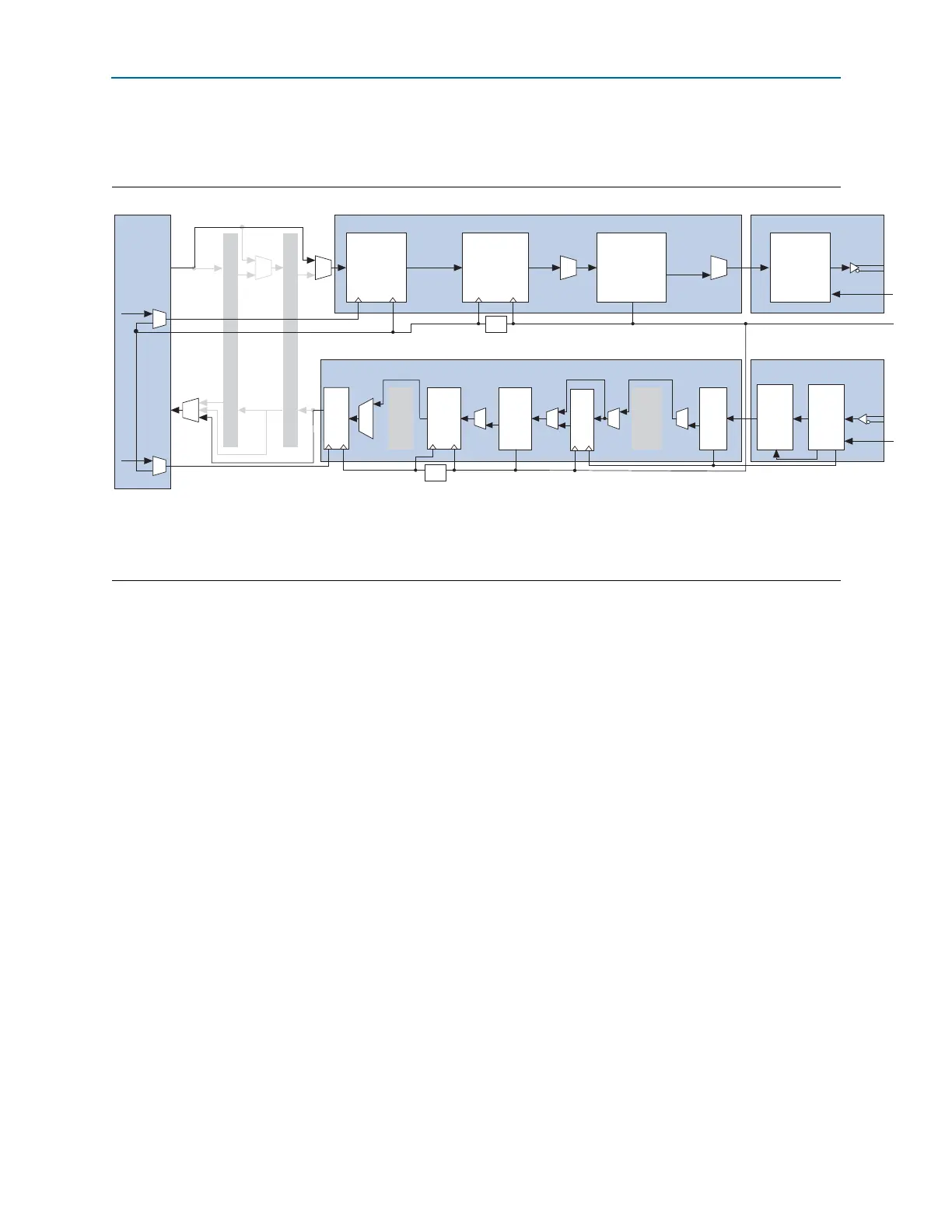

Figure 1–60 shows the transceiver channel datapath and clocking when configured in

Serial RapidIO mode.

Figure 1–60. Transceiver Channel Datapath and Clocking when Configured in Serial RapidIO Mode

Notes to Figure 1–60:

(1) Optional rate match FIFO.

(2) High-speed recovered clock.

(3) Low-speed recovered clock.

(3)

Byte Serializer

8B/10B Encoder

Transmitter Channel PCS Transmitter Channel PMA

Serializer

PCIe Hard IP

FPGA

Fabric

PIPE Interface

Tx Phase

Comp

FIFO

tx_datain

tx_dataout

wr_clk rd_clk

wr_clk rd_clk

high-speed

clock

low-speed clock

tx_coreclk

tx_clkout

rx_coreclk

Receiver Channel PCS Receiver Channel PMA

rx_dataout

rx_datain

Deserial-

izer

CDR

Byte

De-

serializer

Byte

Order-

ing

Deskew

FIFO

8B/10B

Decoder

Rate

Match

FIFO

CDR clock

(2)

Word

Aligner

Rx

Phase

Comp

FIFO

/2

/2

(1)

Loading...

Loading...