Chapter 1: Cyclone IV Transceivers Architecture 1–91

Transceiver Top-Level Port Lists

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

pipestatus Output N/A

PIPE receiver status port.

■ Signal is 3 bits wide and is encoded as follows:

■ 3'b000: Received data OK

■ 3'b001: one SKP symbol added

■ 3'b010: one SKP symbol removed

■ 3'b011: Receiver detected

■ 3'b100: 8B/10B decoder error

■ 3'b101: Elastic buffer overflow

■ 3'b110: Elastic buffer underflow

■ 3'b111: Received disparity error

rx_elecidleinfersel Input N/A

Controls the electrical idle inference mechanism as specified in

Table 1–17 on page 1–57

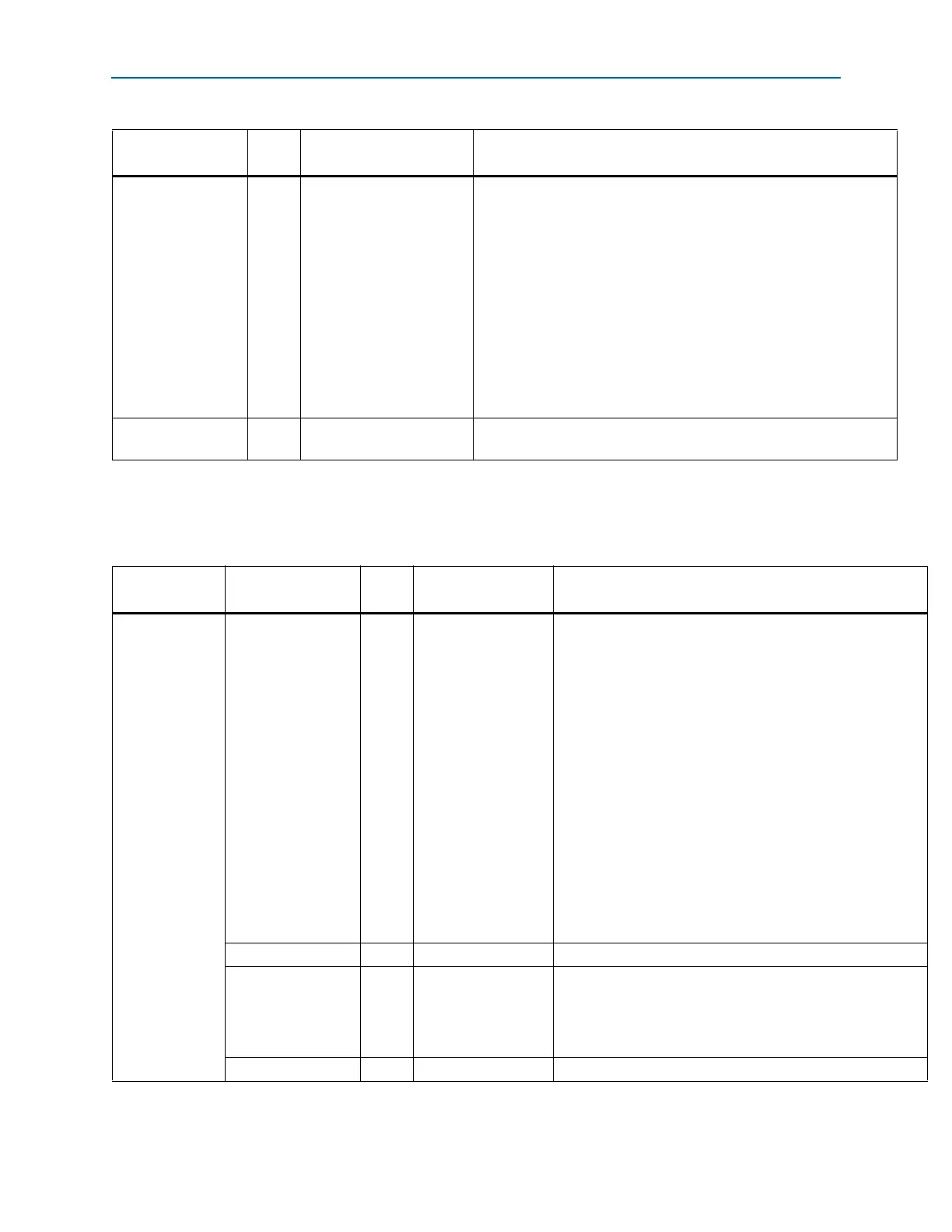

Note to Table 1–28:

(1) For equivalent signals defined in PIPE 2.00 specification, refer to Table 1–15 on page 1–54.

Table 1–28. PIPE Interface Ports in ALTGX Megafunction for Cyclone IV GX

(1)

(Part 2 of 2)

Port Name

Input/

Output

Clock Domain Description

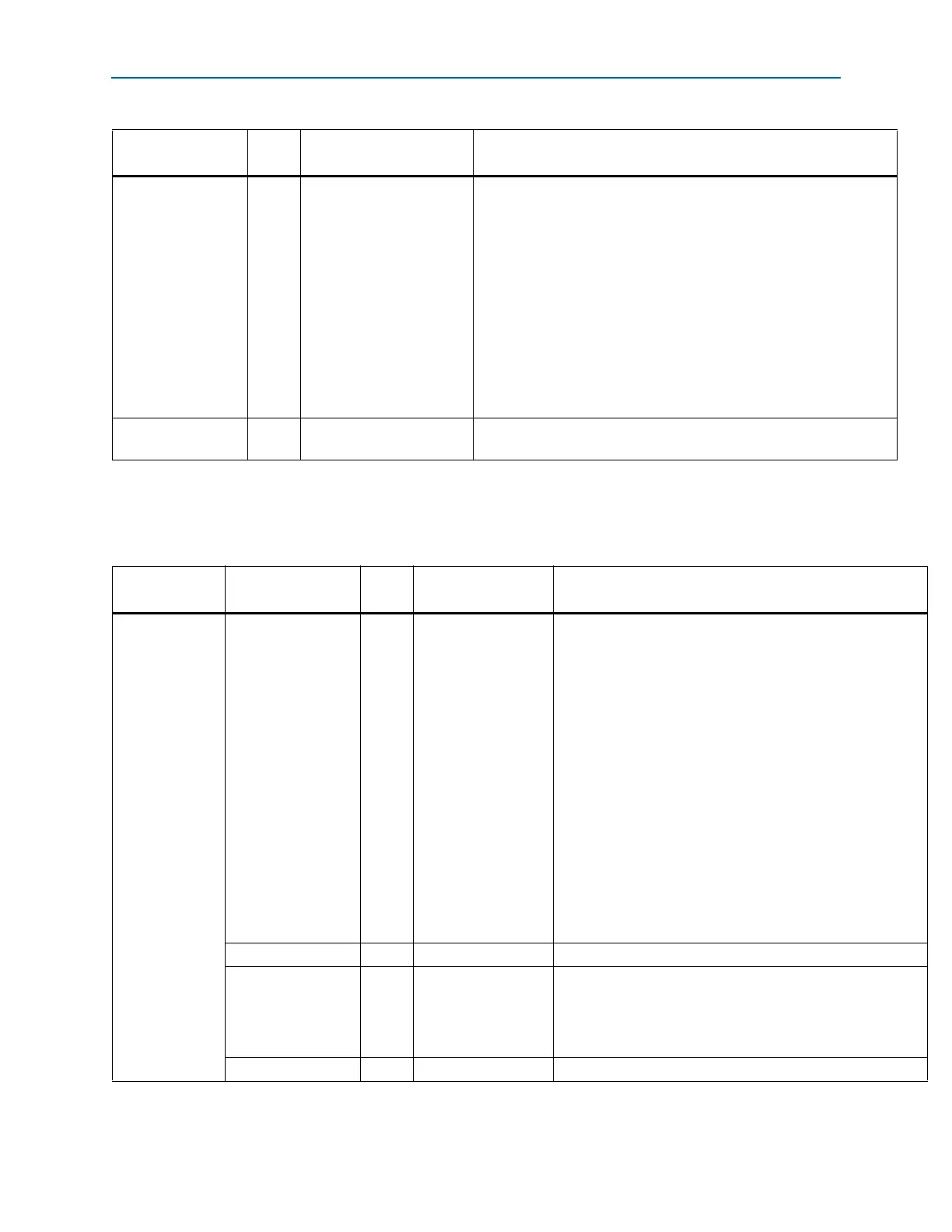

Table 1–29. Multipurpose PLL, General Purpose PLL and Miscellaneous Ports in ALTGX Megafunction for

Cyclone IV GX (Part 1 of 2)

Block Port Name

Input/

Output

Clock Domain Description

PLL

pll_inclk Input Clock signal

Input reference clock for the PLL (multipurpose PLL or

general purpose PLL) used by the transceiver instance. When

configured with the transmitter and receiver channel

configuration in Deterministic Latency mode, multiple

pll_inclk

ports are available as follows.

Configured with PLL PFD feedback—x is the number of

channels selected:

■

pll_inclk[x-1..0]

are input reference clocks for each

transmitter in the transceiver instance

■

pll_inclk[x+1..x]

are input reference clocks for

receivers in the transceiver instance

Configured without PLL PFD feedback:

■

pll_inclk[0]

is input reference clock for transmitters in

the transceiver instance

■

pll_inclk[1]

is input reference clock for receivers in the

transceiver instance

pll_locked Output Asynchronous signal PLL (used by the transceiver instance) lock indicator.

pll_areset Input Asynchronous signal

PLL (used by the transceiver instance) reset.

■ When asserted, the PLL is kept in reset state.

■ When deasserted, the PLL is active and locks to the input

reference clock.

coreclkout Output Clock signal FPGA fabric-transceiver interface clock in bonded modes.

Loading...

Loading...