1–90 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Top-Level Port Lists

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

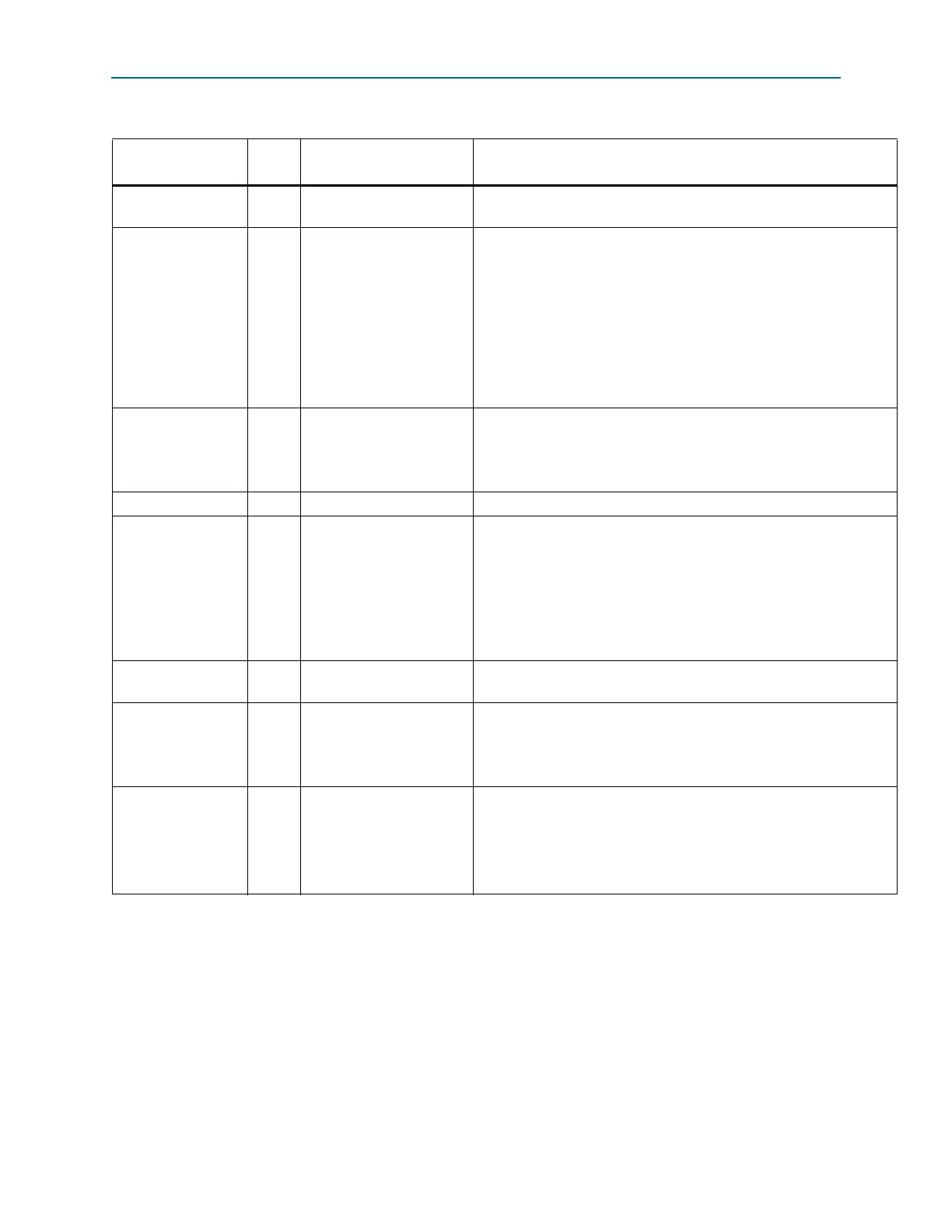

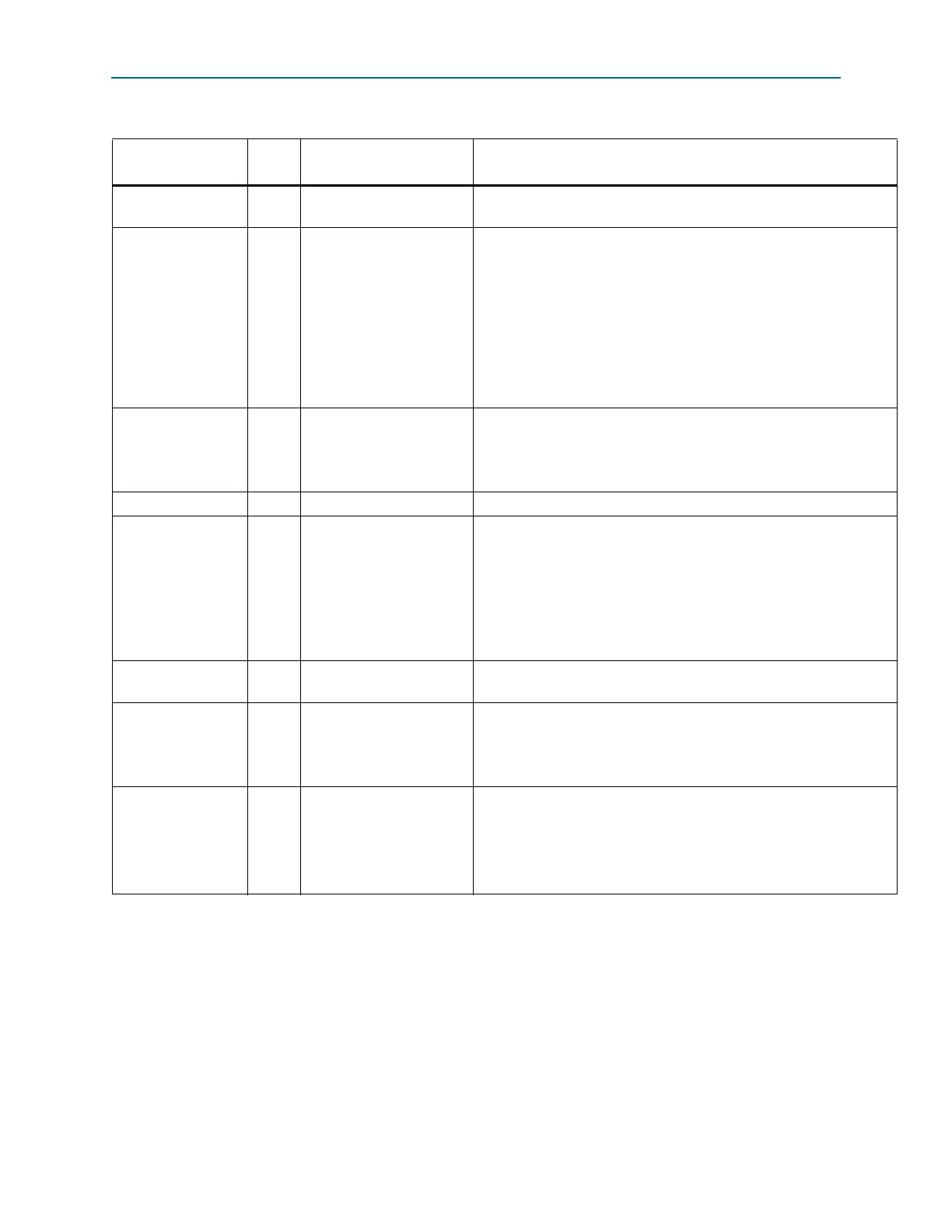

Table 1–28. PIPE Interface Ports in ALTGX Megafunction for Cyclone IV GX

(1)

(Part 1 of 2)

Port Name

Input/

Output

Clock Domain Description

fixedclk Input Clock signal

125-MHz clock for receiver detect and offset cancellation only in PIPE

mode.

tx_detectrxloop Input Asynchronous signal

Receiver detect or reverse parallel loopback control.

■ A high level in the P1 power state and tx_forceelecidle

signal asserted begins the receiver detection operation to determine

if there is a valid receiver downstream. This signal must be

deasserted when the pipephydonestatus signal indicates

receiver detect completion.

■ A high level in the P0 power state with the tx_forceelecidle

signal deasserted dynamically configures the channel to support

reverse parallel loopback mode.

tx_forcedisp

compliance

Input Asynchronous signal

Force the 8B/10B encoder to encode with negative running disparity.

■ Assert only when transmitting the first byte of the PIPE-compliance

pattern to force the 8B/10B encoder with a negative running

disparity.

pipe8b10binvpolarity Input Asynchronous signal Invert the polarity of every bit of the 10-bit input to the 8B/10B decoder

powerdn Input Asynchronous signal

PIPE power state control.

■ Signal is 2 bits wide and is encoded as follows:

■ 2'b00: P0 (Normal operation)

■ 2'b01: P0s (Low recovery time latency, low power state)

■ 2'b10: P1 (Longer recovery time latency, lower power state)

■ 2'b11: P2 (Lowest power state)

pipedatavalid Output N/A

Valid data and control on the rx_dataout and rx_ctrldetect

ports indicator.

pipephydone

status

Output Asynchronous signal

PHY function completion indicator.

■ Asserted for one clock cycle to communicate completion of several

PHY functions, such as power state transition and receiver

detection.

pipeelecidle Output Asynchronous signal

Electrical idle detected or inferred at the receiver indicator.

■ When electrical idle inference is used, this signal is driven high

when it infers an electrical idle condition

■ When electrical idle inference is not used, the

rx_signaldetect signal is inverted and driven on this port.

Loading...

Loading...