Chapter 1: Cyclone IV Transceivers Architecture 1–89

Transceiver Top-Level Port Lists

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

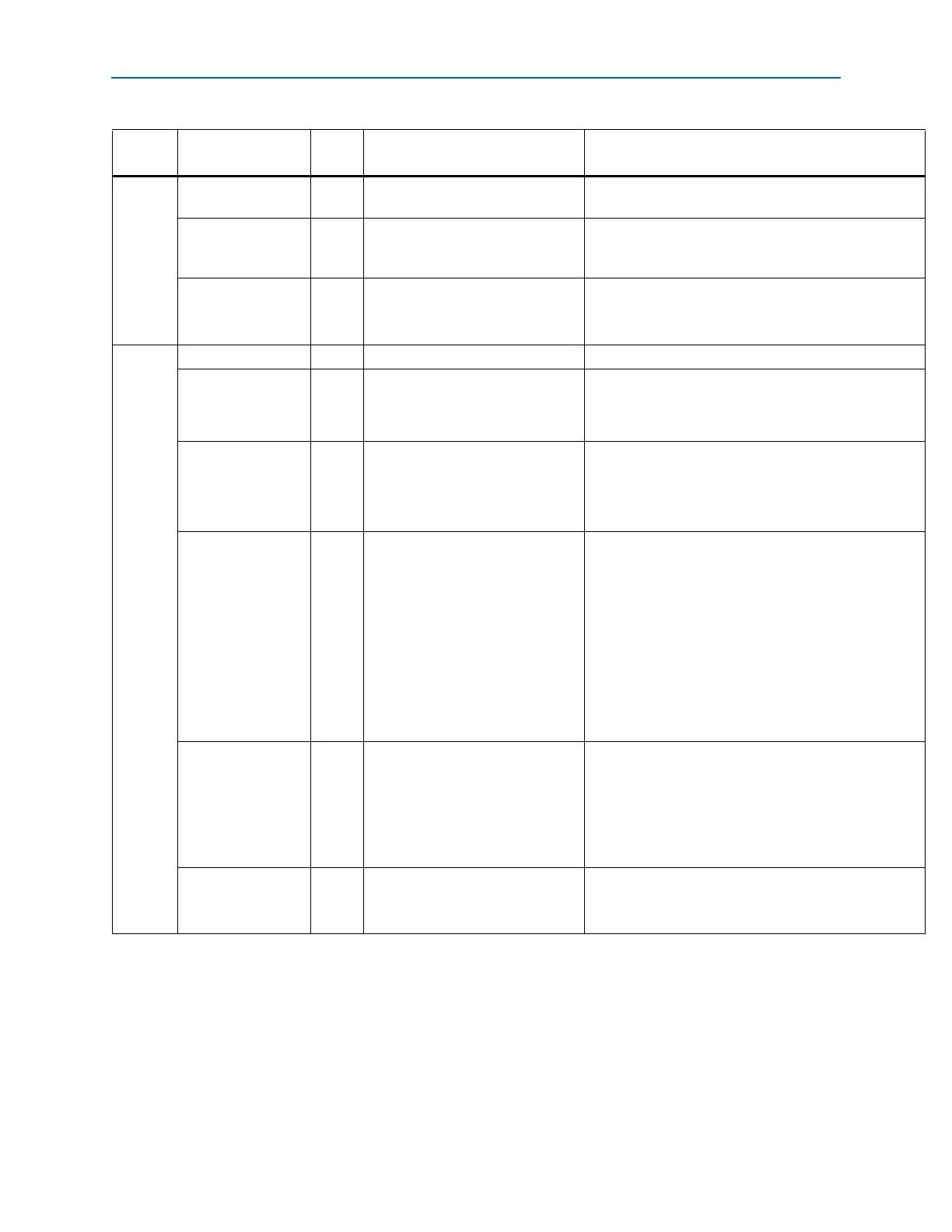

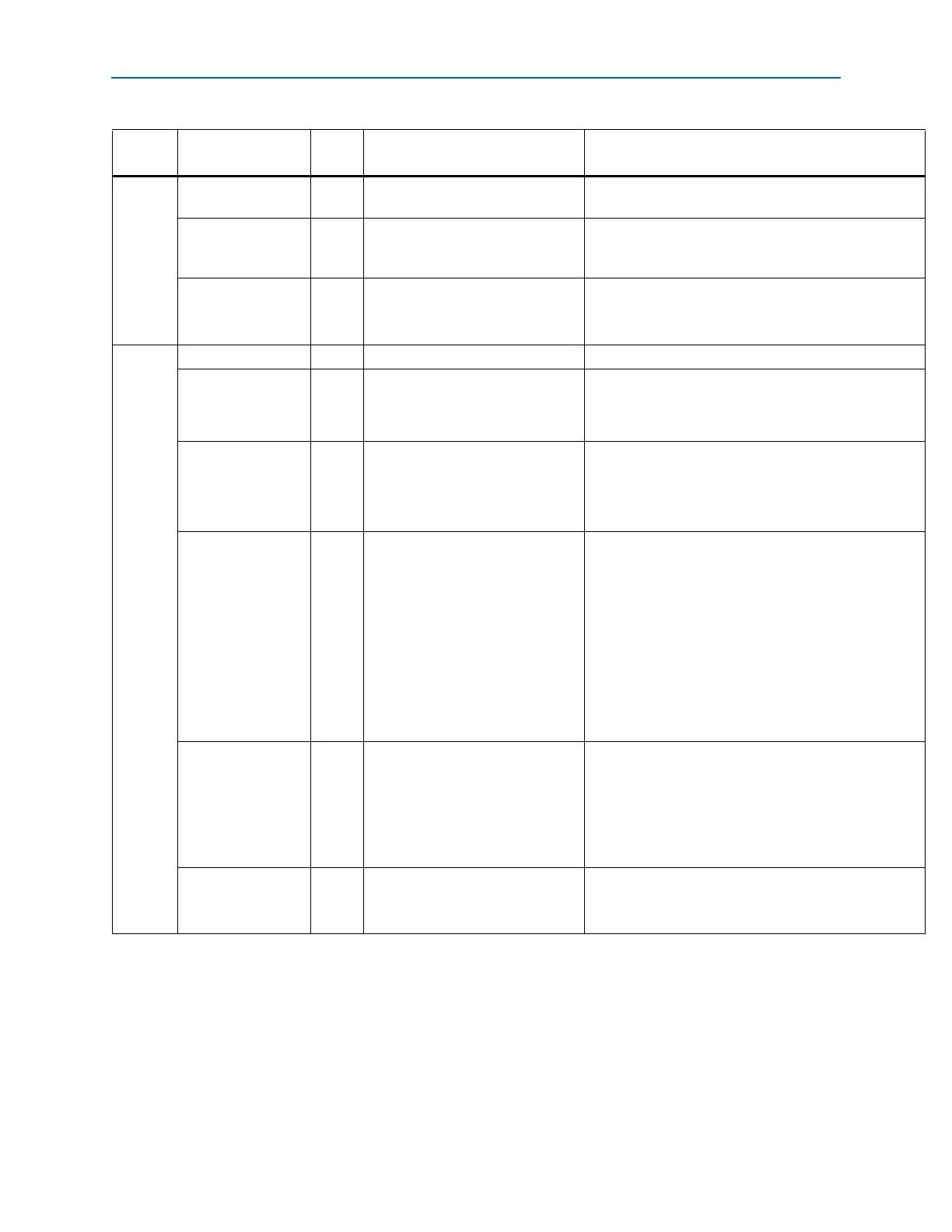

RX PCS

rx_coreclk Output Clock signal

Optional read clock port for the RX phase compensation

FIFO.

rx_phase_comp_fifo

_error

Output

Synchronous to tx_clkout

(non-bonded modes) or

coreclkout (bonded modes)

RX phase compensation FIFO full or empty indicator.

■ A high level indicates FIFO is either full or empty.

rx_bitslipboundarys

electout

Output Asynchronous signal.

Indicate the number of bits slipped in the word aligner

configured in manual alignment mode.

■ Values range from 0 to 9.

RX PMA

rx_datain Input N/A Receiver serial data input port.

rx_freqlocked Output Asynchronous signal

Receiver CDR lock state indicator

■ A high level indicates the CDR is in LTD state.

■ A low level indicates the CDR is in LTR state.

rx_locktodata Input Asynchronous signal

Receiver CDR LTD state control signal

■ A high level forces the CDR to LTD state

■ When deasserted, the receiver CDR lock state

depends on the rx_locktorefclk signal level.

rx_locktorefclk Input Asynchronous signal

Receiver CDR LTR state control signal.

■ The rx_locktorefclk and rx_locktodata

signals control whether the receiver CDR states as

follows:

[rx_locktodata:rx_locktorefclk]

■ 2'b00—receiver CDR is in automatic lock mode

■ 2b'01—receiver CDR is in manual lock mode (LTR

state)

■ 2b'1x—receiver CDR is in manual lock mode (LTD

state)

rx_signaldetect Output Asynchronous signal

Signal threshold detect indicator.

■ Available in Basic mode when 8B/10B

encoder/decoder is used, and in PIPE mode.

■ A high level indicates that the signal present at the

receiver input buffer is above the programmed signal

detection threshold value.

rx_recovclkout Output Clock signal

CDR low-speed recovered clock

■ Only available in the GIGE mode for applications such

as Synchronous Ethernet.

Table 1–27. Receiver Ports in ALTGX Megafunction for Cyclone IV GX (Part 3 of 3)

Block Port Name

Input/

Output

Clock Domain Description

Loading...

Loading...