1–88 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Top-Level Port Lists

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

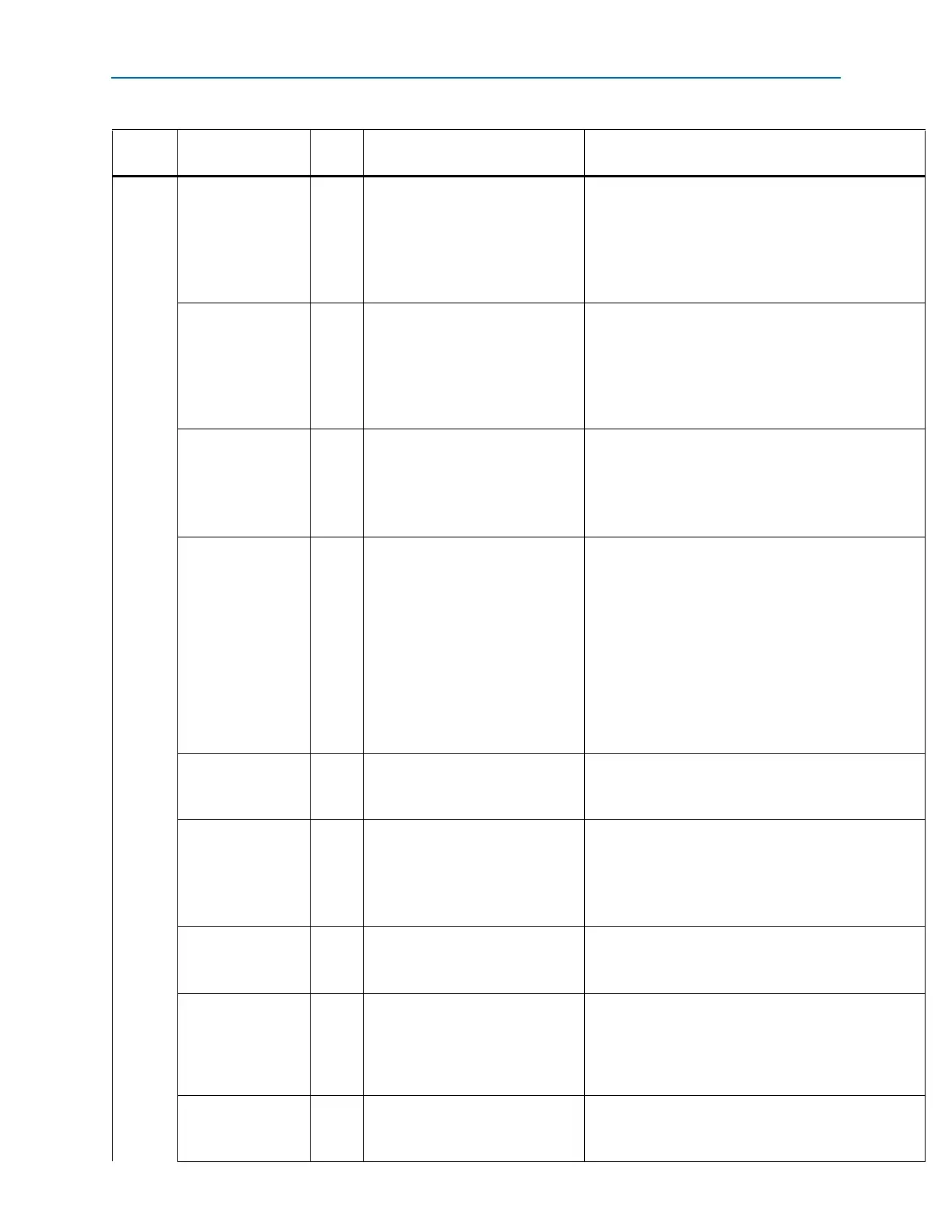

RX PCS

rx_rmfifofull Output

Synchronous to tx_clkout

(non-bonded modes) or

coreclkout (bonded modes)

Rate match FIFO full status indicator.

■ A high level indicates the rate match FIFO is full.

■ Driven for a minimum of two serial clock cycles in

configurations without a byte serializer and a

minimum of three recovered clock cycles in

configurations with a byte serializer.

rx_rmfifoempty Output

Synchronous to tx_clkout

(non-bonded modes) or

coreclkout (bonded modes)

Rate match FIFO empty status indicator.

■ A high level indicates the rate match FIFO is empty.

■ Driven for a minimum of two serial clock cycles in

configurations without a byte serializer and a

minimum of three recovered clock cycles in

configurations with a byte serializer.

rx_ctrldetect Output

Synchronous to tx_clkout

(non-bonded modes) or

coreclkout (bonded modes)

8B/10B decoder control or data identifier.

■ A high level indicates received code group is a /Kx.y/

control code group.

■ A low level indicates received code group is a /Dx.y/

data code group.

rx_errdetect Output

Synchronous to tx_clkout

(non-bonded modes) or

coreclkout (bonded modes)

8B/10B code group violation or disparity error indicator.

■ A high level indicates that a code group violation or

disparity error was detected on the associated

received code group.

■ Use with the rx_disperr signal to differentiate

between a code group violation or a disparity error as

follows: [rx_errdetect:rx_disperr]

■ 2'b00—no error

■ 2'b10—code group violation

■ 2'b11—disparity error or both

rx_disperr Output

Synchronous to tx_clkout

(non-bonded modes) or

coreclkout (bonded modes)

8B/10B disparity error indicator.

■ A high level indicates that a disparity error was

detected on the associated received code group.

rx_runningdisp Output

Synchronous to tx_clkout

(non-bonded modes) or

coreclkout (bonded modes)

8B/10B current running disparity indicator.

■ A high level indicates a positive current running

disparity at the end of the decoded byte

■ A low level indicates a negative current running

disparity at the end of the decoded byte

rx_enabyteord Input Asynchronous signal

Enable byte ordering control

■ A low-to-high transition triggers the byte ordering

block to restart byte ordering operation.

rx_byteorder

alignstatus

Output

Synchronous to tx_clkout

(non-bonded modes) or

coreclkout (bonded modes)

Byte ordering status indicator.

■ A high level indicates that the byte ordering block has

detected the programmed byte ordering pattern in the

least significant byte of the received data from the

byte deserializer.

rx_dataout Output

Synchronous to tx_clkout

(non-bonded modes) or

coreclkout (bonded modes)

Parallel data output from the receiver to the FPGA fabric.

■ Bus width depends on channel width multiplied by

number of channels per instance.

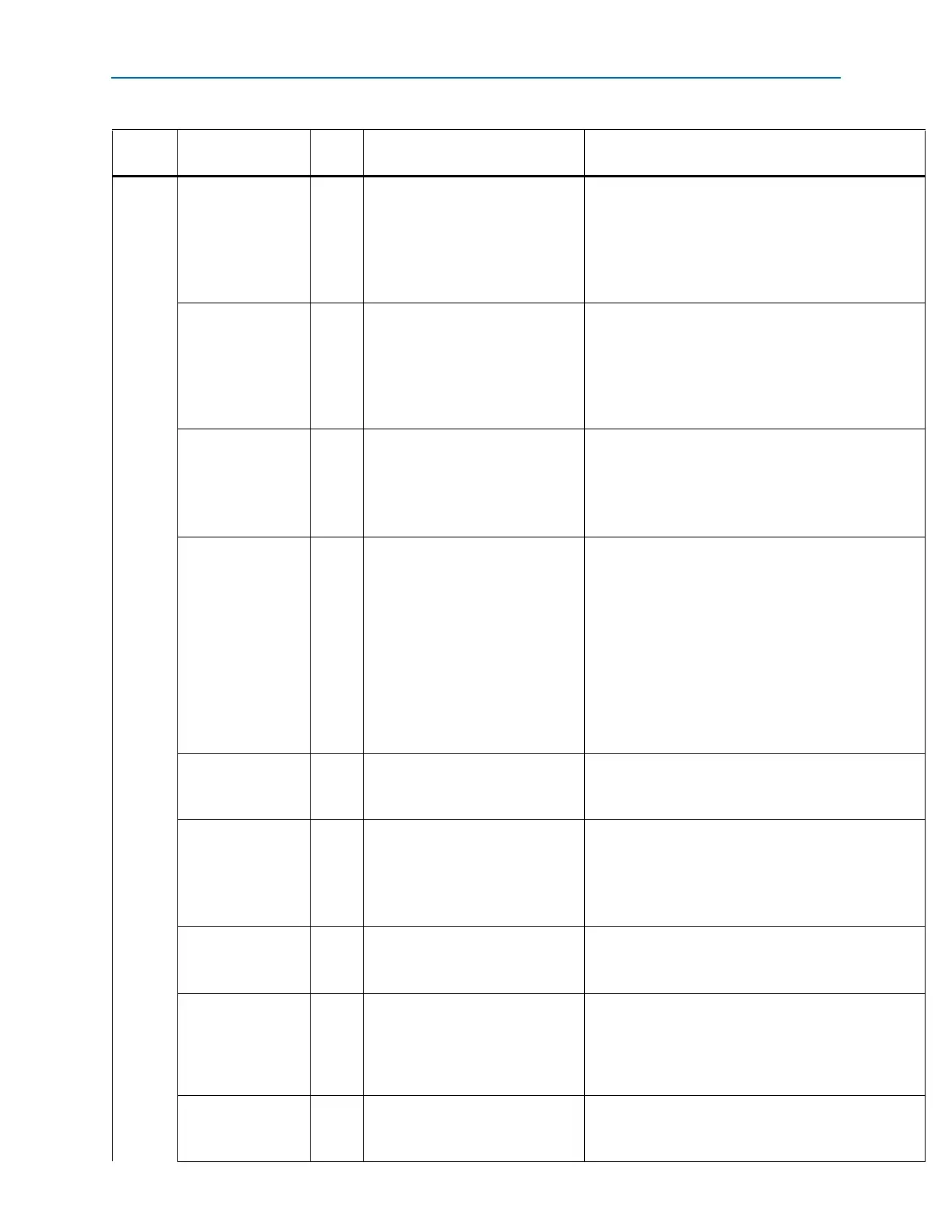

Table 1–27. Receiver Ports in ALTGX Megafunction for Cyclone IV GX (Part 2 of 3)

Block Port Name

Input/

Output

Clock Domain Description

Loading...

Loading...