Chapter 1: Cyclone IV Transceivers Architecture 1–87

Transceiver Top-Level Port Lists

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

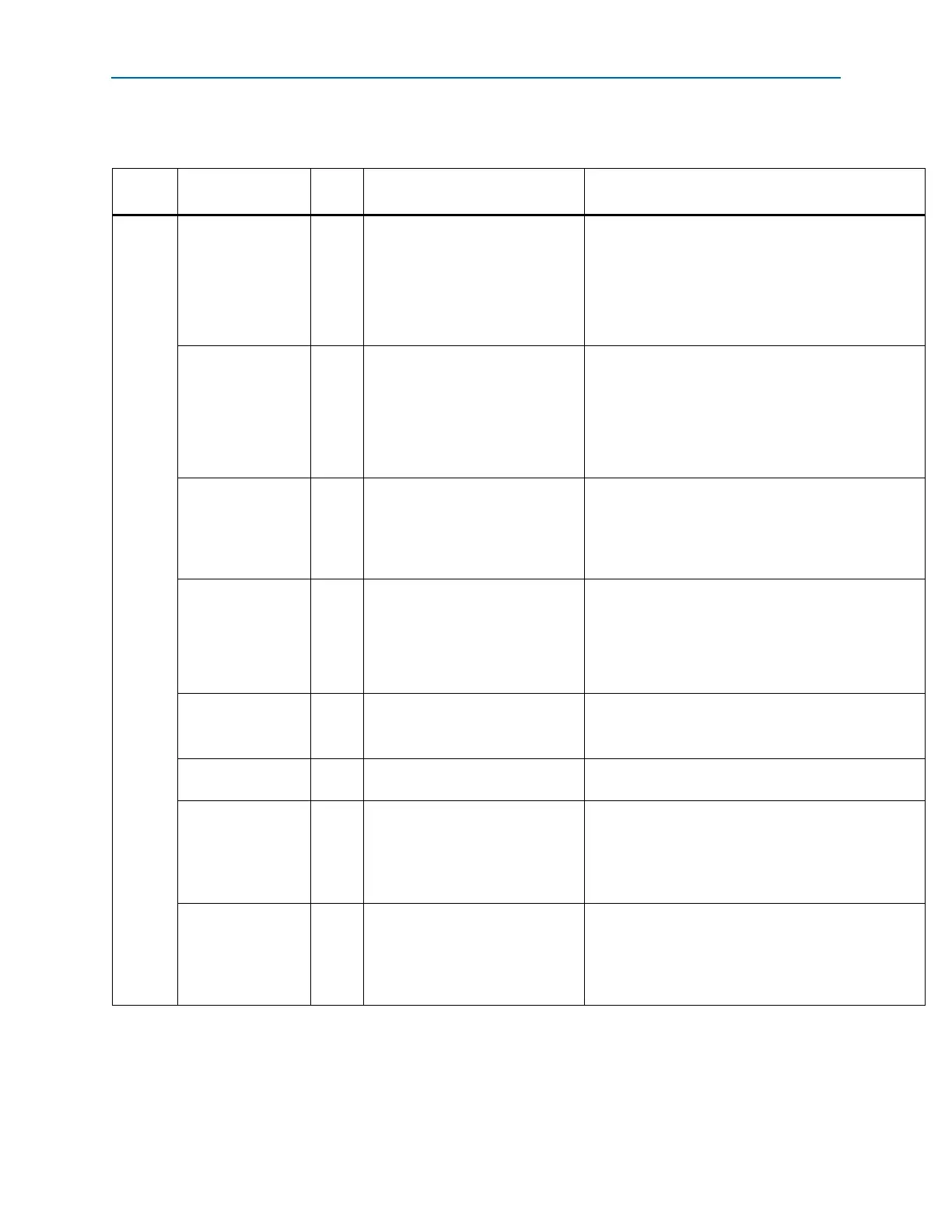

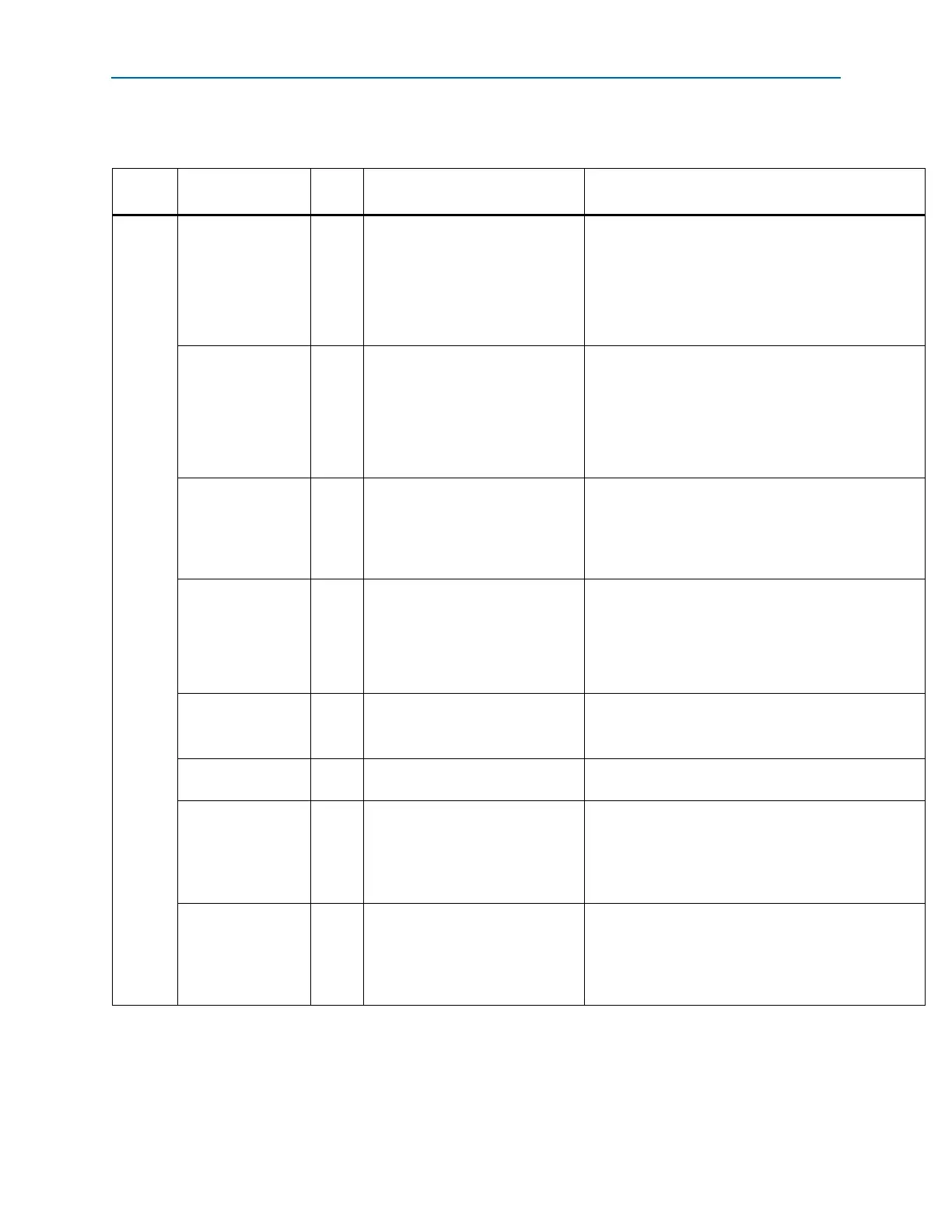

Table 1–27. Receiver Ports in ALTGX Megafunction for Cyclone IV GX (Part 1 of 3)

Block Port Name

Input/

Output

Clock Domain Description

RX PCS

rx_syncstatus Output

Synchronous to

tx_clkout

(non-

bonded modes with rate match

FIFO),

rx_clkout

(non-bonded

modes without rate match FIFO),

coreclkout

(bonded modes), or

rx_coreclk

(when using the

optional

rx_coreclk

input)

Word alignment synchronization status indicator. This

signal passes through the RX Phase Compensation FIFO.

■ Not available in bit-slip mode

rx_patternde

tect

Output

Synchronous to

tx_clkout

(non-

bonded modes with rate match

FIFO),

rx_clkout

(non-bonded

modes without rate match FIFO),

coreclkout

(bonded modes), or

rx_coreclk

(when using the

optional

rx_coreclk

input)

Indicates when the word alignment logic detects the

alignment pattern in the current word boundary. This

signal passes through the RX Phase Compensation FIFO.

rx_bitslip Input

Asynchronous signal. Minimum

pulse width is two

parallel clock cycles.

Bit-slip control for the word aligner configured in bit-slip

mode.

■ At every rising edge, word aligner slips one bit into

the received data stream, effectively shifting the word

boundary by one bit.

rx_rlv Output

Asynchronous signal. Driven for a

minimum of two recovered clock

cycles in configurations without

byte serializer and a minimum of

three recovered clock cycles in

configurations with byte serializer.

Run-length violation indicator.

■ A high pulse indicates that the number of consecutive

1s or 0s in the received data stream exceeds the

programmed run length violation threshold.

rx_invpolarity Input

Asynchronous signal. Minimum

pulse width is two parallel clock

cycles.

Generic receiver polarity inversion control.

■ A high level to invert the polarity of every bit of the 8-

or 10-bit data to the word aligner.

rx_enapattern

align

Input Asynchronous signal.

Controls the word aligner operation configured in

manual alignment mode.

rx_rmfifodata

inserted

Output

Synchronous to tx_clkout

(non-bonded modes) or

coreclkout (bonded modes)

Rate match FIFO insertion status indicator.

■ A high level indicates the rate match pattern byte is

inserted to compensate for the ppm difference in the

reference clock frequencies between the upstream

transmitter and the local receiver.

rx_rmfifodata

deleted

Output

Synchronous to tx_clkout

(non-bonded modes) or

coreclkout (bonded modes)

Rate match FIFO deletion status indicator.

■ A high level indicates the rate match pattern byte is

deleted to compensate for the ppm difference in the

reference clock frequencies between the upstream

transmitter and the local receiver.

Loading...

Loading...