1–86 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Top-Level Port Lists

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

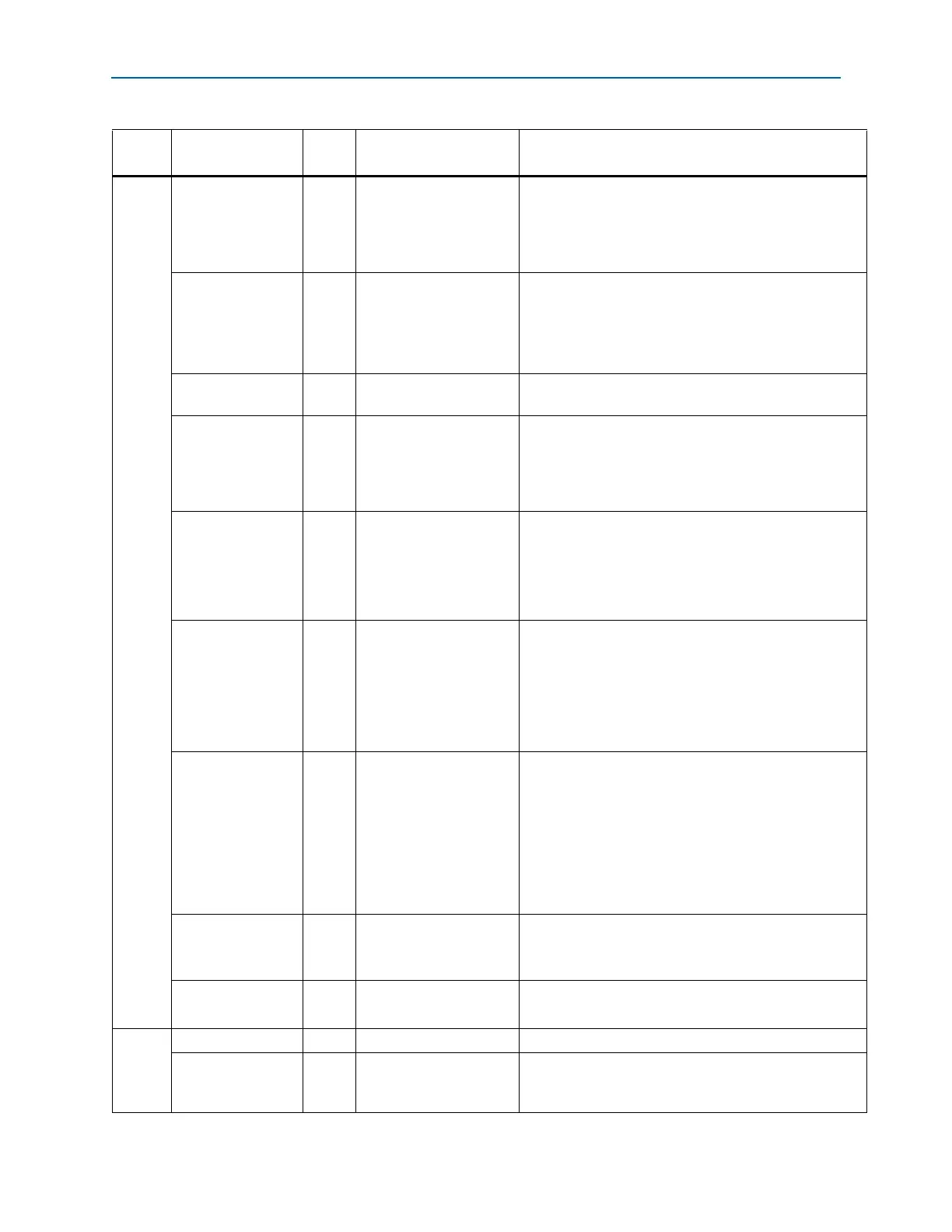

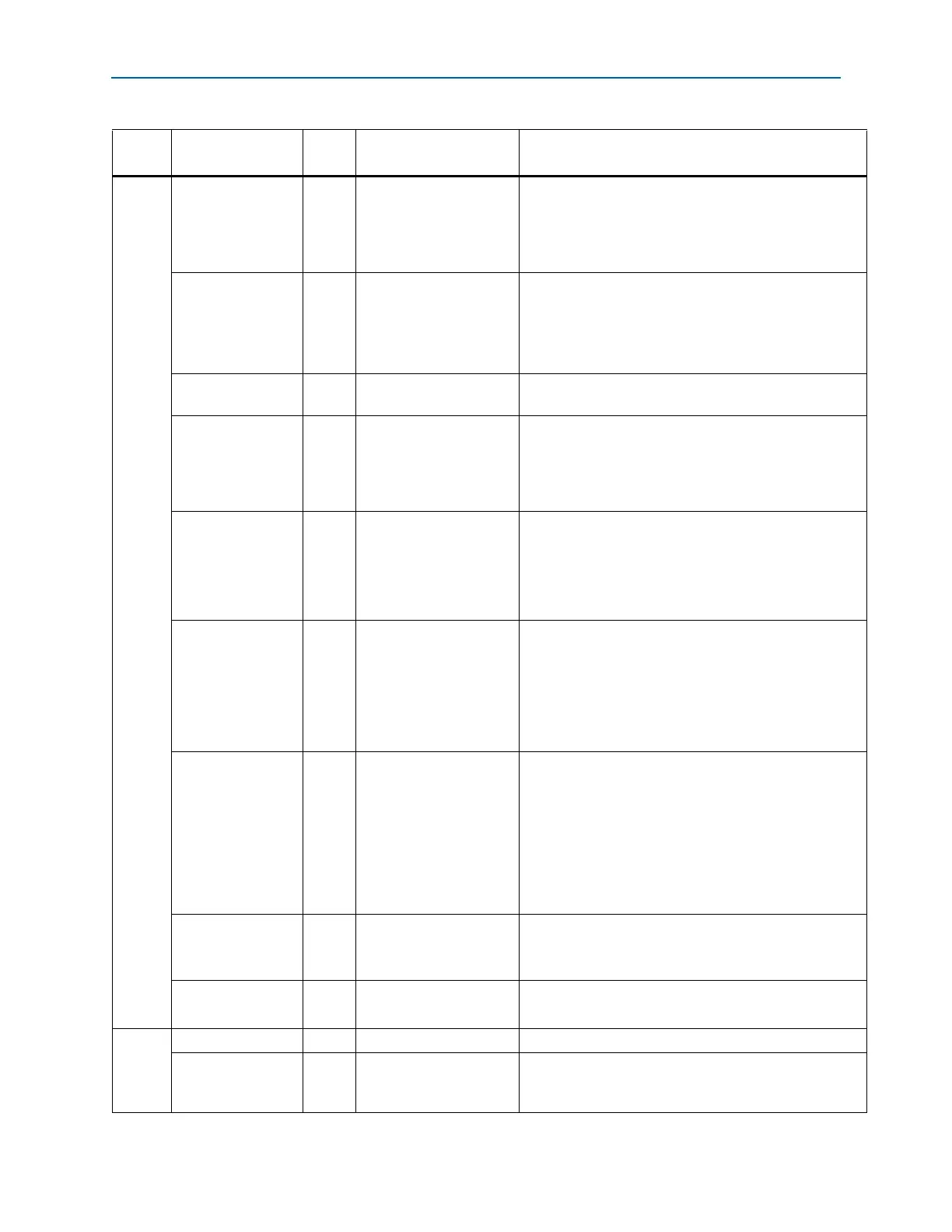

Table 1–26. Transmitter Ports in ALTGX Megafunction for Cyclone IV GX

Block Port Name

Input/

Output

Clock Domain Description

TX PCS

tx_datain Input

Synchronous to

tx_clkout (non-

bonded modes) or

coreclkout (bonded

modes)

Parallel data input from the FPGA fabric to the transmitter.

■ Bus width depends on channel width multiplied by

number of channels per instance.

tx_clkout Output Clock signal

FPGA fabric-transmitter interface clock in non-bonded

modes

■ Each channel has a tx_clkout signal that can be

used to clock data (tx_datain) from the FPGA

fabric into the transmitter.

tx_coreclk Input Clock signal

Optional write clock port for the TX phase compensation

FIFO.

tx_phase_comp_fifo

_error

Output

Synchronous to

tx_clkout (non-

bonded modes) or

coreclkout (bonded

modes)

TX phase compensation FIFO full or empty indicator.

■ A high level indicates FIFO is either full or empty.

tx_ctrlenable Input

Synchronous to

tx_clkout (non-

bonded modes) or

coreclkout (bonded

modes)

8B/10B encoder control or data identifier. This signal

passes through the TX Phase Compensation FIFO.

■ A high level to encode data as a /Kx.y/ control code

group.

■ A low level to encode data as a /Dx.y/ data code group.

tx_forcedisp Input

Synchronous to

tx_clkout (non-

bonded

modes) or

coreclkout

(bonded modes)

8B/10B encoder forcing disparity control. This signal

passes through the TX Phase Compensation FIFO.

■ A high level to force encoding to positive or negative

disparity depending on the tx_dispval signal level.

■ A low level to allow default encoding according to the

8B/10B running disparity rules.

tx_dispval Input

Synchronous to

tx_clkout (non-

bonded

modes) or

coreclkout

(bonded modes)

8B/10B encoder forcing disparity value. This signal

passes through the TX Phase Compensation FIFO.

■ A high level to force encoding with a negative disparity

code group when tx_forcedisp port is asserted

high.

■ A low level to force encoding with a positive disparity

code group when tx_forcedisp port is asserted

high.

tx_invpolarity Input

Asynchronous signal.

Minimum pulse width is

two parallel clock cycles.

Transmitter polarity inversion control.

■ A high level to invert the polarity of every bit of the 8-

or 10-bit input data to the serializer.

tx_bitslipboundarys

elect

Input Asynchronous signal.

Control the number of bits to slip before serializer.

■ Valid values from 0 to 9

TX PMA

tx_dataout Output — Transmitter serial data output signal.

tx_forceelec

idle

Input Asynchronous signal.

Force the transmitter buffer to PIPE electrical idle signal

levels. For equivalent signal defined in PIPE 2.00

specification, refer to Table 1–15 on page 1–54.

Loading...

Loading...