Chapter 1: Cyclone IV Transceivers Architecture 1–49

Transceiver Functional Modes

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

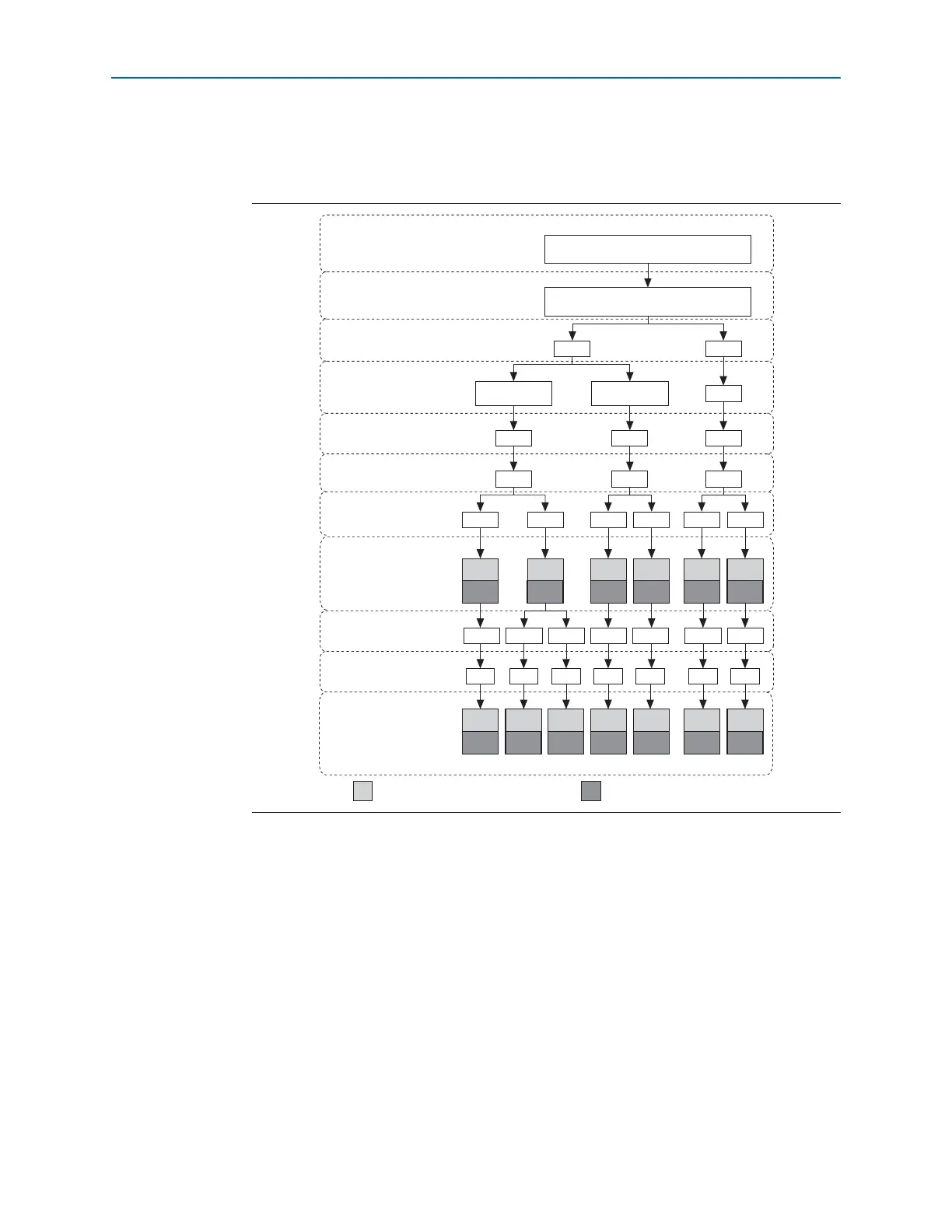

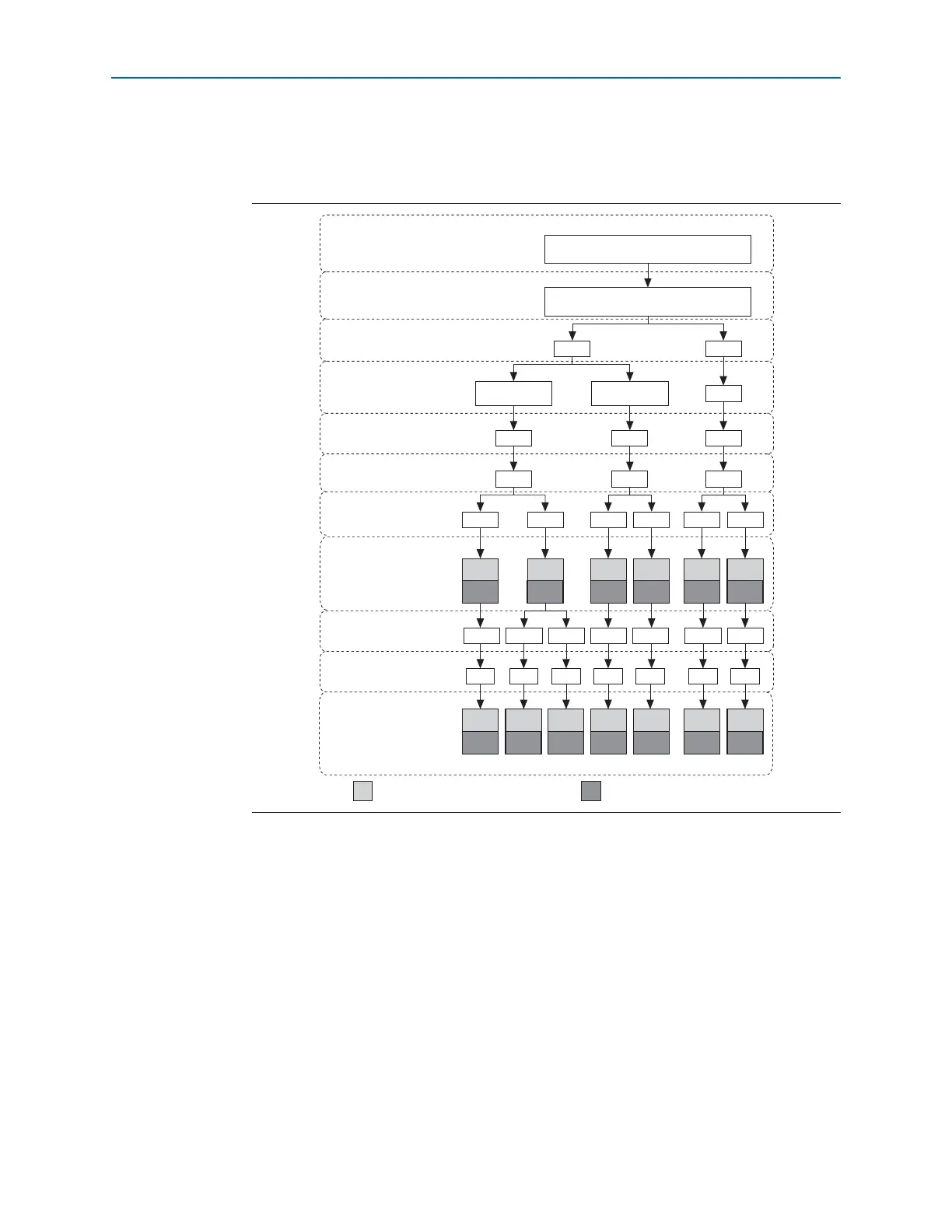

Figure 1–45 and Figure 1–46 show the supported transceiver configurations in Basic

mode with the 8-bit and 10-bit PMA-PCS interface width respectively.

Figure 1–45. Supported Transceiver Configurations in Basic Mode with the 8-bit PMA-PCS

Interface Width

Functional Mode

Channel Bonding

Low-Latency PCS

Word Aligner (Pattern Length)

8B/10B Encoder/Decoder

Rate Match FIFO

Byte SERDES

Byte Ordering

FPGA Fabric-to-Transceiver

Interface Width

FPGA Fabric-to-Transceiver

Interface Frequency (MHz)

8-Bit

Disabled Enabled

0.6-

1.0

0.6-

1.25

0.6-

2.0

0.6-

2.5

0.6-

1.0

0.6-

1.25

0.6-

1.0

0.6-

2.5

0.6-

1.0

0.6-

1.25

0.6-

1.0

0.6-

1.25

Disabled Enabled

Manual Alignment

(16-Bit)

Bit Slip

(16-Bit)

Disabled

Disabled

Disabled

Disabled

8-Bit16-Bit 16-Bit 16-Bit 8-Bit 16-Bit

Basic (8-Bit PMA-PCS Interface Width)

×1, ×2, ×4

DisabledDisabled

Disabled

Disabled

Disabled Disabled

Disabled Enabled

Disabled Enabled

Disabled Enabled

Disabled

Disabled

Applicable for devices in

F324 and smaller packages

Applicable for devices in

F484 and larger packages

Data Rate (Gbps)

75-

125

75-

156.25

75-

125

75-

156.25

75-

125

75-

156.25

37.5-

125

37.5-

156.25

37.5-

125

37.5-

156.25

37.5-

125

37.5-

156.25

37.5-

125

37.5-

156.25

Loading...

Loading...