Chapter 3: Cyclone IV Dynamic Reconfiguration 3–5

Dynamic Reconfiguration Controller Port List

November 2011 Altera Corporation Cyclone IV Device Handbook,

Volume 2

FPGA Fabric and ALTGX_RECONFIG Interface Signals

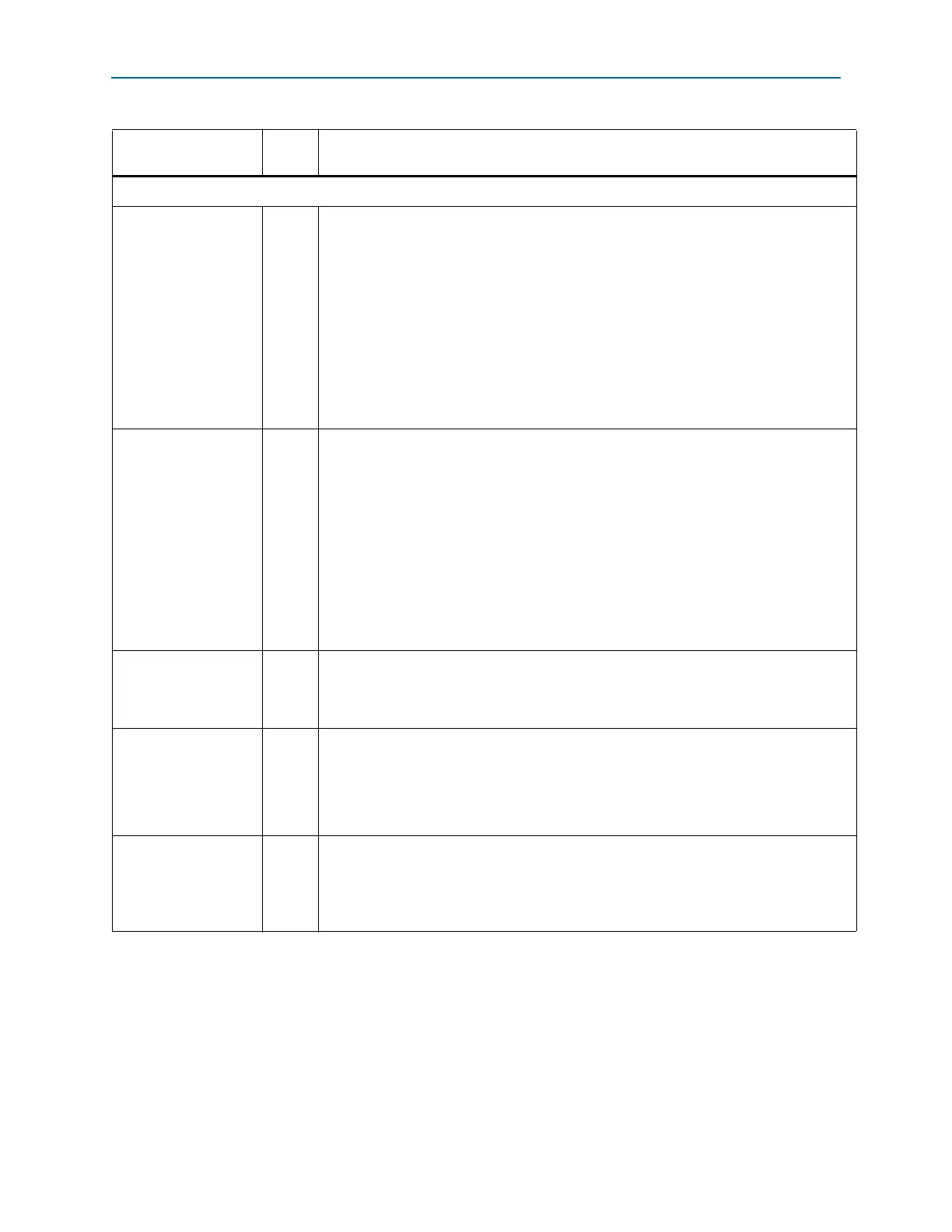

write_all

Input

Assert this signal for one

reconfig_clk

clock cycle to initiate a write transaction from the

ALTGX_RECONFIG instance to the ALTGX instance.

You can use this signal in two ways for .mif-based modes:

■ Continuous write operation—select the Enable continuous write of all the words

needed for reconfiguration option to pulse the

write_all

signal only once for writing

a whole .mif. The What is the read latency of the MIF contents option is available for

selection in this case only. Enter the desired latency in terms of the

reconfig_clk

cycles.

■ Regular write operation—when the Enable continuous write of all the words needed

for reconfiguration option is disabled, every word of the .mif requires its own write

cycle.

busy

Output

This signal is used to indicate the busy status of the dynamic reconfiguration controller

during offset cancellation. After the device powers up, this signal remains low for the first

reconfig_clk

clock cycle. It then is asserted and remains high when the dynamic

reconfiguration controller performs offset cancellation on all the receiver channels

connected to the ALTGX_RECONFIG instance.

Deassertion of the

busy

signal indicates the successful completion of the offset

cancellation process.

■ PMA controls reconfiguration mode—this signal is high when the dynamic

reconfiguration controller performs a read or write transaction.

■ Channel reconfiguration modes—this signal is high when the dynamic reconfiguration

controller writes the .mif into the transceiver channel.

read

Input

Assert this signal for one

reconfig_clk

clock cycle to initiate a read transaction. The

read

port is applicable only to the PMA controls reconfiguration mode. The

read

port is

available when you select Analog controls in the Reconfiguration settings screen and

select at least one of the PMA control ports in the Analog controls screen.

data_valid

Output

Applicable only to PMA controls reconfiguration mode. This port indicates the validity of

the data read from the transceiver by the dynamic reconfiguration controller.

The data on the output read ports is valid only when the

data_valid

is high.

This signal is enabled when you enable at least one PMA control port used in read

transactions, for example

tx_vodctrl_out

.

error

Output

This indicates that an unsupported operation was attempted. You can select this in the

Error checks screen. The dynamic reconfiguration controller deasserts the

busy

signal and

asserts the

error

signal for two

reconfig_clk

cycles when you attempt an unsupported

operation. For more information, refer to “Error Indication During Dynamic

Reconfiguration” on page 3–36.

Table 3–2. Dynamic Reconfiguration Controller Port List (ALTGX_RECONFIG Instance) (Part 2 of 7)

Port Name

Input/

Output

Description

Loading...

Loading...