240 KByte Flash Module (S12FTMRG240K2V1)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 1135

All bits in the FCLKDIV register are readable, bit 7 is not writable, bit 6 is write-once-hi and controls the

writability of the FDIV field in normal mode. In special mode, bits 6-0 are writable any number of times

but bit 7 remains unwritable.

CAUTION

The FCLKDIV register should never be written while a Flash command is

executing (CCIF=0).

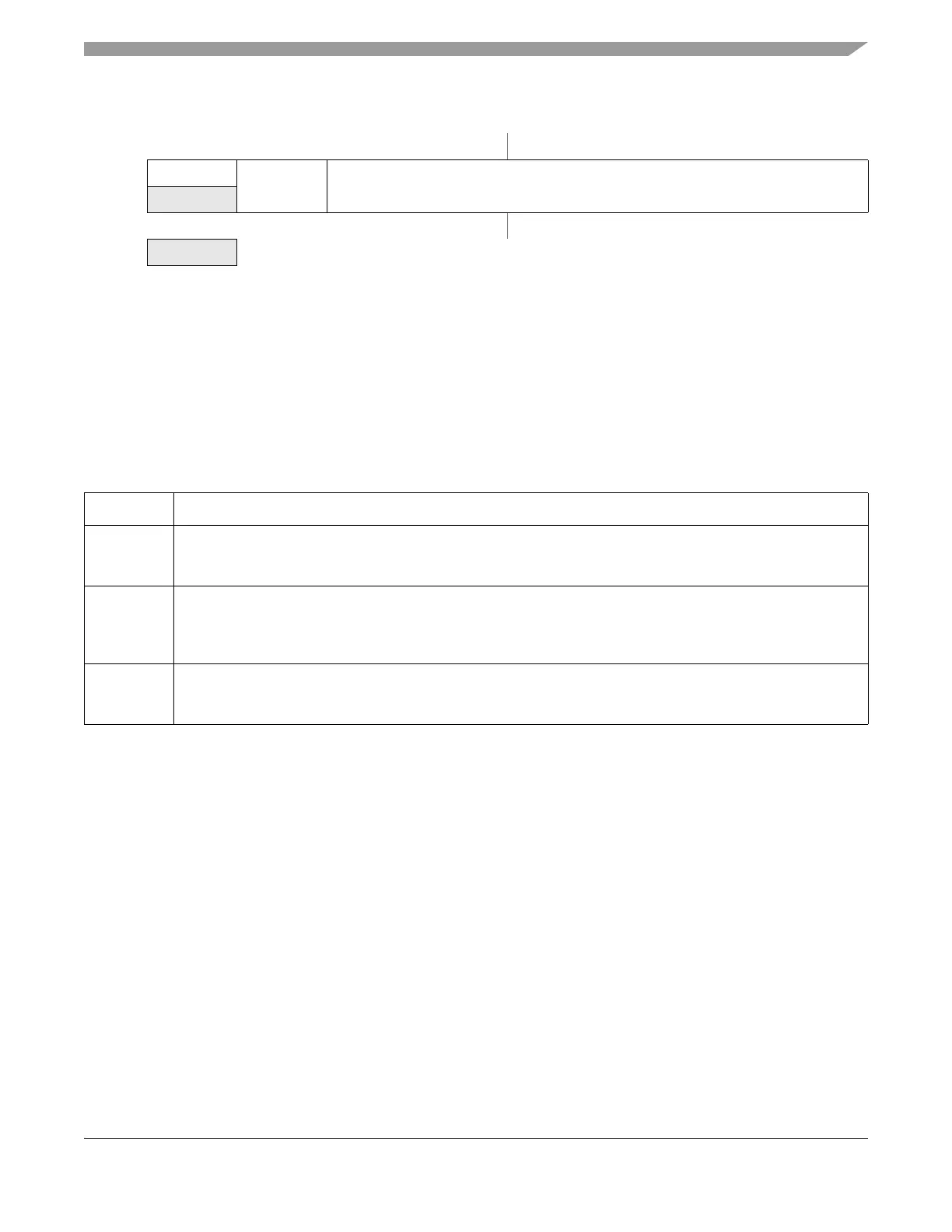

Offset Module Base + 0x0000

76543210

RFDIVLD

FDIVLCK FDIV[5:0]

W

Reset00000000

= Unimplemented or Reserved

Figure 31-5. Flash Clock Divider Register (FCLKDIV)

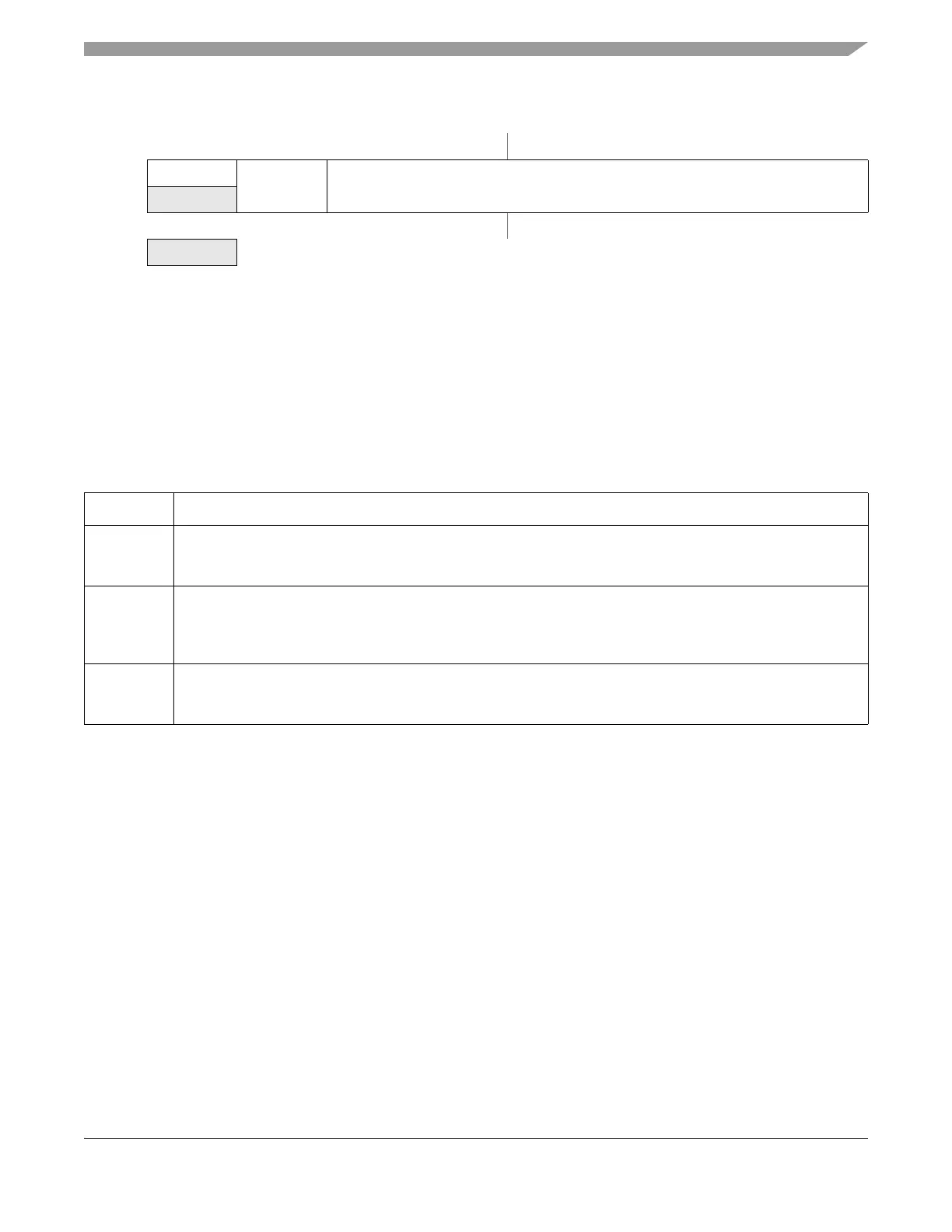

Table 31-7. FCLKDIV Field Descriptions

Field Description

7

FDIVLD

Clock Divider Loaded

0 FCLKDIV register has not been written since the last reset

1 FCLKDIV register has been written since the last reset

6

FDIVLCK

Clock Divider Locked

0 FDIV field is open for writing

1 FDIV value is locked and cannot be changed. Once the lock bit is set high, only reset can clear this bit and

restore writability to the FDIV field in normal mode.

5–0

FDIV[5:0]

Clock Divider Bits — FDIV[5:0] must be set to effectively divide BUSCLK down to 1 MHz to control timed events

during Flash program and erase algorithms. Table 31-8 shows recommended values for FDIV[5:0] based on the

BUSCLK frequency. Please refer to Section 31.4.4, “Flash Command Operations,” for more information.

Loading...

Loading...