Electrical Characteristics

MC9S12G Family Reference Manual Rev.1.27

1214 NXP Semiconductors

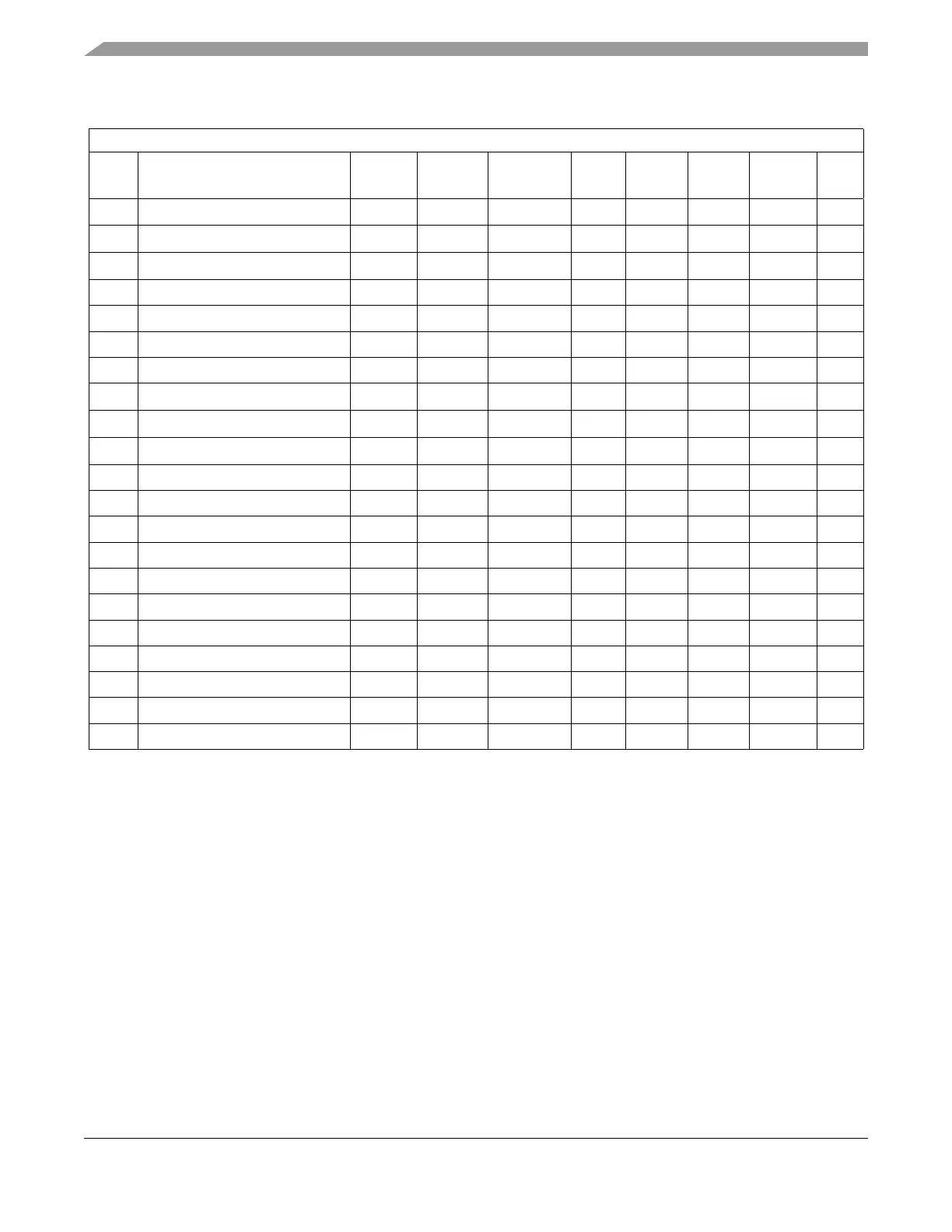

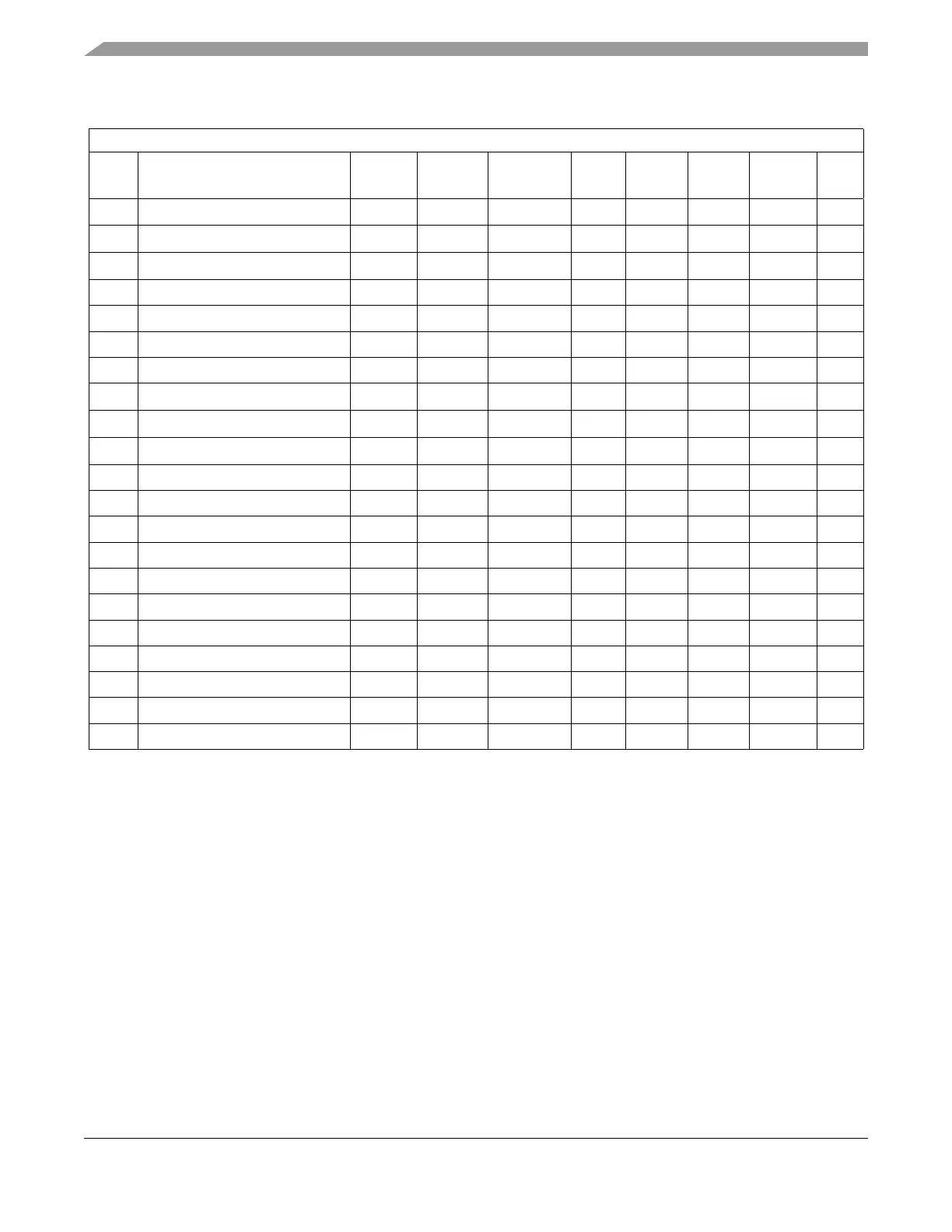

Table A-36. NVM Timing Characteristics)

, S12GN48, S12G48, S12G64, S12GA64

Num Command

f

NVMOP

cycle

f

NVMBUS

cycle

Symbol Min

1

Typ

2

Max

3

Lfmax

4

Unit

1

Erase Verify All Blocks

5,6

0 17937

t

RD1ALL

0.72 0.72 1.43 35.87 ms

2

Erase Verify Block (Pflash)

5

0 16924

t

RD1BLK_P

0.68 0.68 1.35 33.85 ms

3

Erase Verify Block (EEPROM)

6

01512

t

RD1BLK_D

0.06 0.06 0.12 3.02 ms

4 Erase Verify P-Flash Section 0 476

t

RD1SEC

19.04 19.04 38.08 952 ms

5 Read Once 0 445

t

RDONCE

17.8 17.8 17.8 445 s

6 Program P-Flash (4 Word) 164 2925

t

PGM_4

0.27 0.28 0.63 11.91 ms

7 Program Once 164 2888

t

PGMONCE

0.27 0.28 0.28 3.09 ms

8

Erase All Blocks

5,6

100066 18273

t

ERSALL

96.03 100.8 101.53 161.63 ms

9

Erase Flash Block (Pflash)

5

100060 17157

t

ERSBLK_P

95.98 100.75 101.43 159.39 ms

10

Erase Flash Block (EEPROM)

6

100060 1808

t

ERSBLK_D

95.37 100.13 100.2 128.69 ms

11 Erase P-Flash Sector 20015 865

t

ERSPG

19.1 20.05 20.08 26.75 ms

12 Unsecure Flash 100066 18351

t

UNSECU

96.03 100.8 101.53 161.78 ms

13 Verify Backdoor Access Key 0 481

t

VFYKEY

19.24 19.24 19.24 481 s

14 Set User Margin Level 0 399

t

MLOADU

15.96 15.96 15.96 399 s

15 Set Factory Margin Level 0 408

t

MLOADF

16.32 16.32 16.32 408 s

16 Erase Verify EEPROM Section 0 546

t

DRD1SEC

0.02 0.02 0.04 1.09 ms

17 Program EEPROM (1 Word) 68 1565

t

DPGM_1

0.13 0.13 0.32 6.35 ms

18 Program EEPROM (2 Word) 136 2512

t

DPGM_2

0.23 0.24 0.54 10.22 ms

19 Program EEPROM (3 Word) 204 3459

t

DPGM_3

0.33 0.34 0.76 14.09 ms

20 Program EEPROM (4 Word) 272 4406

t

DPGM_4

0.44 0.45 0.98 17.96 ms

21 Erase EEPROM Sector 5015 753

t

DERSPG

4.81 5.05 20.57 37.88 ms

1

Minimum times are based on maximum f

NVMOP

and maximum f

NVMBUS

2

Typical times are based on typical f

NVMOP

and typical f

NVMBUS

3

Maximum times are based on typical f

NVMOP

and typical f

NVMBUS

plus aging

4

Lowest-frequency max times are based on minimum f

NVMOP

and minimum f

NVMBUS

plus aging

5

Affected by Pflash size

6

Affected by EEPROM size

Loading...

Loading...