Port Integration Module (S12GPIMV1)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 239

2.4.3.63 Port AD Interrupt Flag Register (PIF0AD)

Table 2-88. PIE1AD Register Field Descriptions

Field Description

7-0

PIE1AD

Port AD interrupt enable—

This bit enables or disables the edge sensitive pin interrupt on the associated pin. An interrupt can be generated if

the pin is operating in input or output mode when in use with the general-purpose or related peripheral function.

1 Interrupt is enabled

0 Interrupt is disabled (interrupt flag masked)

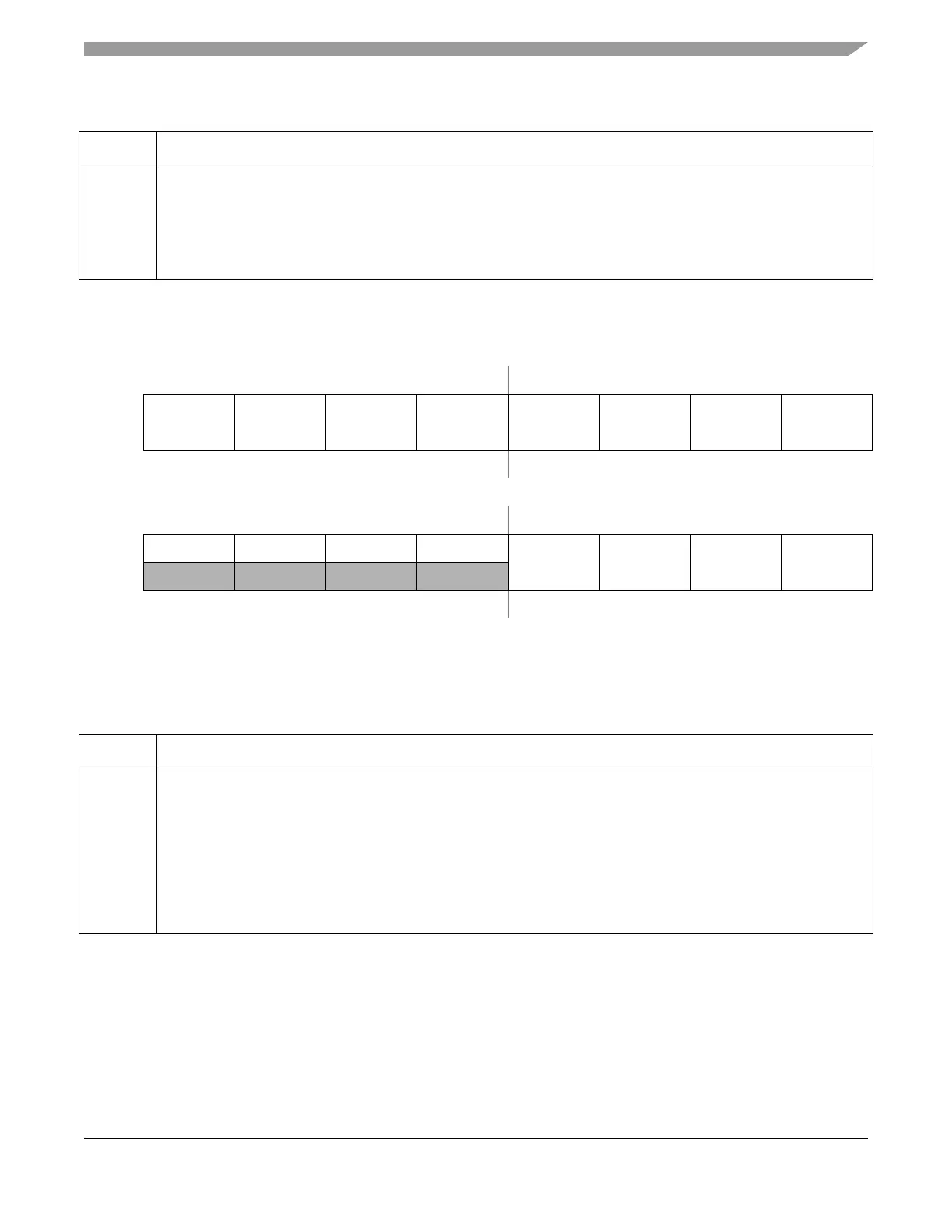

Address 0x027E (G1, G2) Access: User read/write

1

1

Read: Anytime

Write: Anytime, write 1 to clear

76543210

R

PIF0AD7 PIF0AD6 PIF0AD5 PIF0AD4 PIF0AD3 PIF0AD2 PIF0AD1 PIF0AD0

W

Reset00000000

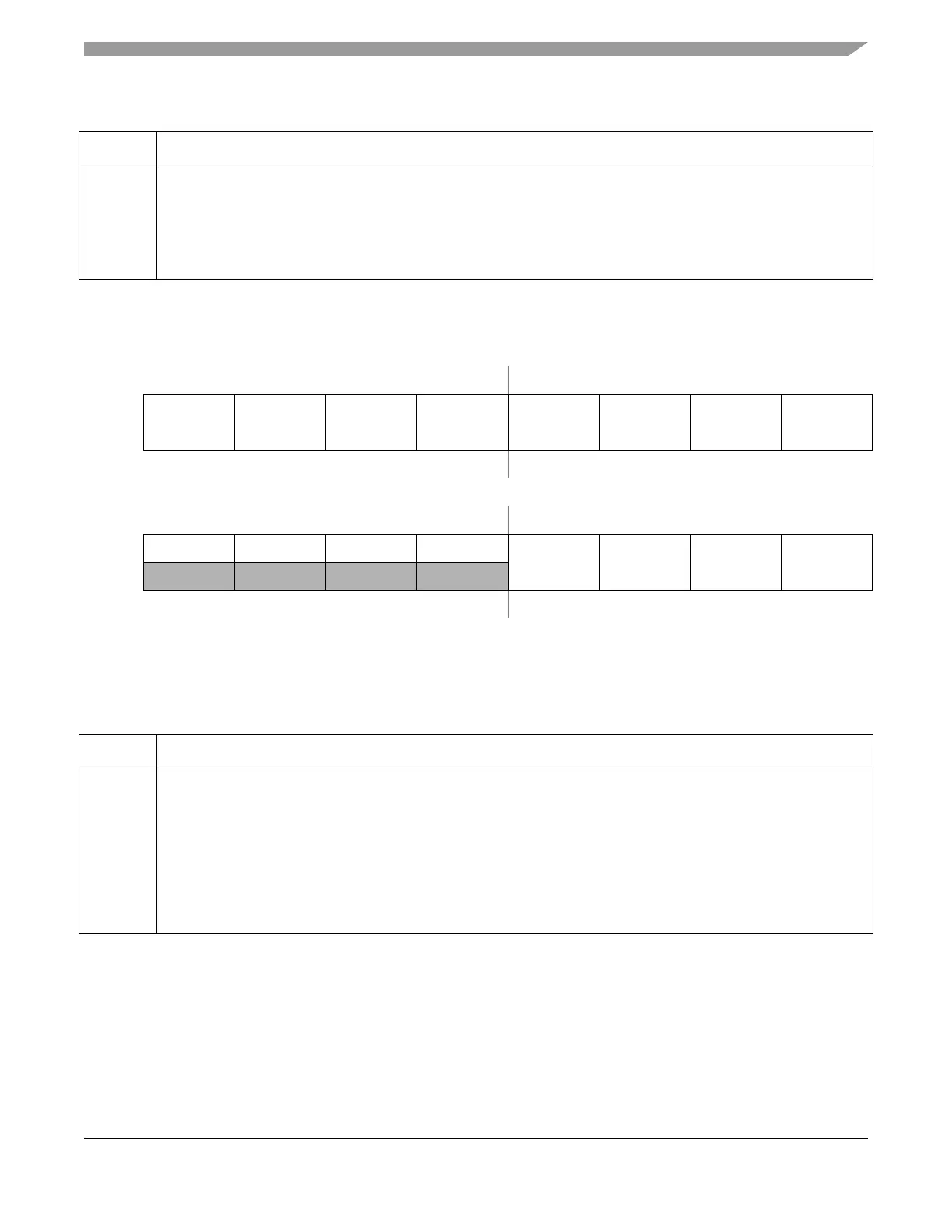

Address 0x027E (G3) Access: User read/write

1

76543210

R0000

PIF0AD3 PIF0AD2 PIF0AD1 PIF0AD0

W

Reset00000000

Figure 2-62. Port AD Interrupt Flag Register (PIF0AD)

Table 2-89. PIF0AD Register Field Descriptions

Field Description

7-0

PIF0AD

Port AD interrupt flag—

This flag asserts after a valid active edge was detected on the related pin (see Section 2.5.4.2, “Pin Interrupts and

Wakeup”). This can be a rising or a falling edge based on the state of the polarity select register. An interrupt will

occur if the associated interrupt enable bit is set.

Writing a logic “1” to the corresponding bit field clears the flag.

1 Active edge on the associated bit has occurred

0 No active edge occurred

Loading...

Loading...