S12S Debug Module (S12SDBGV2)

MC9S12G Family Reference Manual Rev.1.27

336 NXP Semiconductors

8.4.5.4 Trace Buffer Organization (Compressed Pure PC mode)

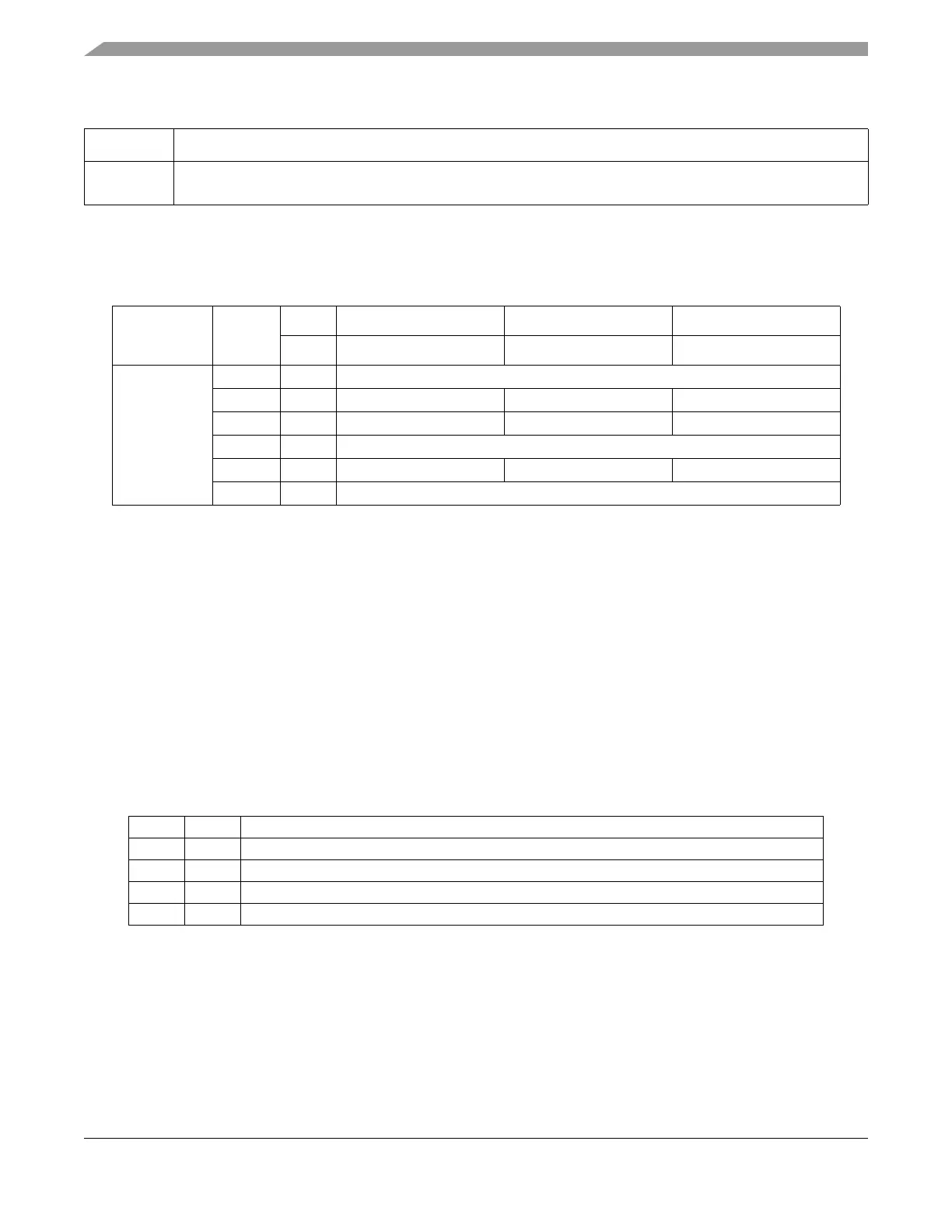

Table 8-40. Trace Buffer Organization Example (Compressed PurePC mode)

NOTE

Configured for end aligned triggering in compressed PurePC mode, then

after rollover it is possible that the oldest base address is overwritten. In this

case all entries between the pointer and the next base address have lost their

base address following rollover. For example in Table 8-40 if one line of

rollover has occurred, Line 1, PC1, is overwritten with a new entry. Thus the

entries on Lines 2 and 3 have lost their base address. For reconstruction of

program flow the first base address following the pointer must be used, in

the example, Line 4. The pointer points to the oldest entry, Line 2.

Field3 Bits in Compressed Pure PC Modes

Each time that PC[17:6] differs from the previous base PC[17:6], then a new base address is stored. The

base address zero value is the lowest address in the 64 address range

The first line of the trace buffer always gets a base PC address, this applies also on rollover.

0

PC16

Program Counter bit 16— In Normal and Loop1 mode this bit corresponds to program counter bit 16.

Mode

Line

Number

2-bits 6-bits 6-bits 6-bits

Field 3 Field 2 Field 1 Field 0

Compressed

Pure PC Mode

Line 1 00 PC1 (Initial 18-bit PC Base Address)

Line 2 11 PC4 PC3 PC2

Line 3 01 0 0 PC5

Line 4 00 PC6 (New 18-bit PC Base Address)

Line 5 10 0 PC8 PC7

Line 6 00 PC9 (New 18-bit PC Base Address)

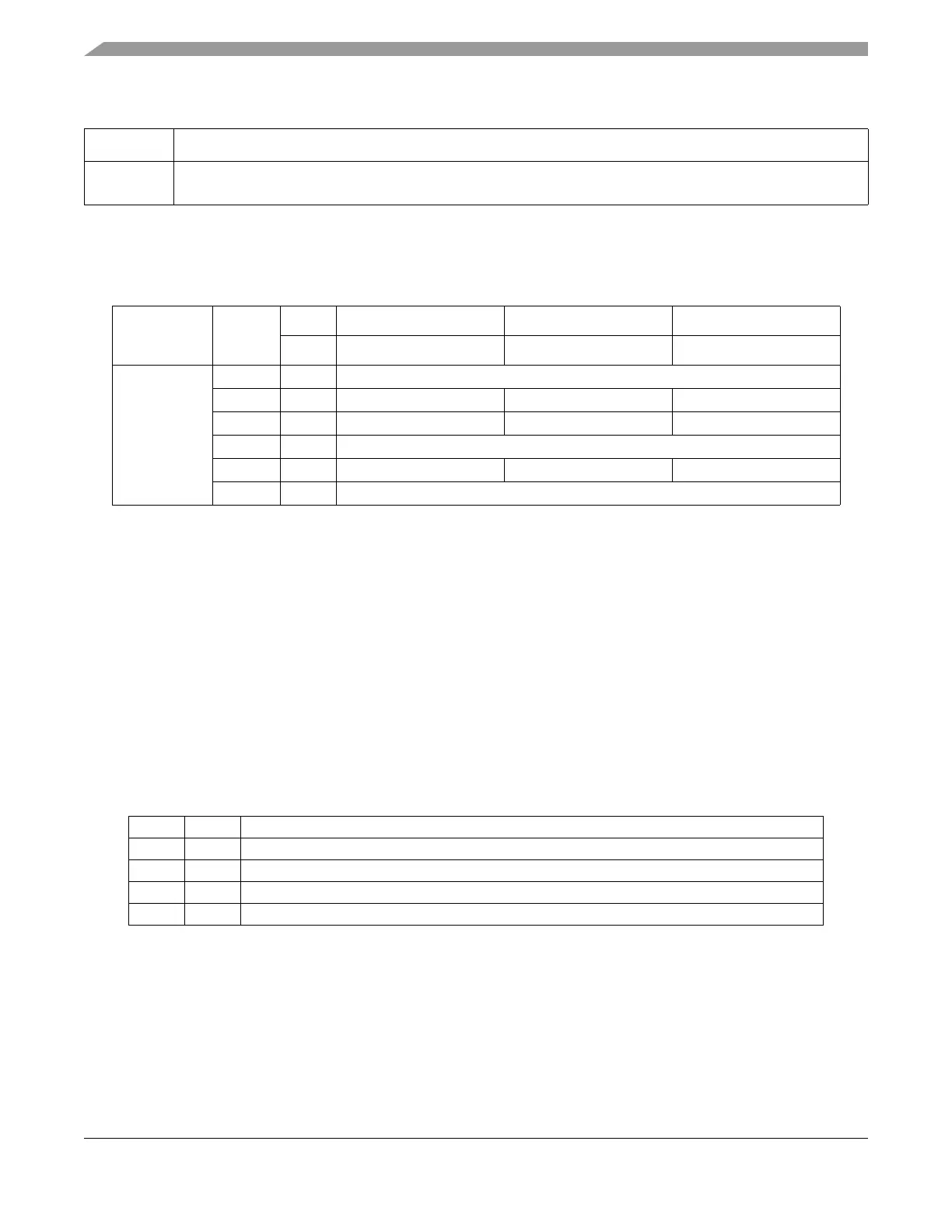

Table 8-41. Compressed Pure PC Mode Field 3 Information Bit Encoding

INF1 INF0 TRACE BUFFER ROW CONTENT

0 0 Base PC address TB[17:0] contains a full PC[17:0] value

0 1 Trace Buffer[5:0] contain incremental PC relative to base address zero value

1 0 Trace Buffer[11:0] contain next 2 incremental PCs relative to base address zero value

1 1 Trace Buffer[17:0] contain next 3 incremental PCs relative to base address zero value

Table 8-39. PCH Field Descriptions (continued)

Bit Description

Loading...

Loading...