S12 Clock, Reset and Power Management Unit (S12CPMU)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 383

10.3.2.18 S12CPMU IRC1M Trim Registers (CPMUIRCTRIMH / CPMUIRCTRIML)

Read: Anytime

Write: Anytime if PROT=0 (CPMUPROT register). Else write has no effect

NOTE

Writes to these registers while PLLSEL=1 clears the LOCK and UPOSC

status bits.

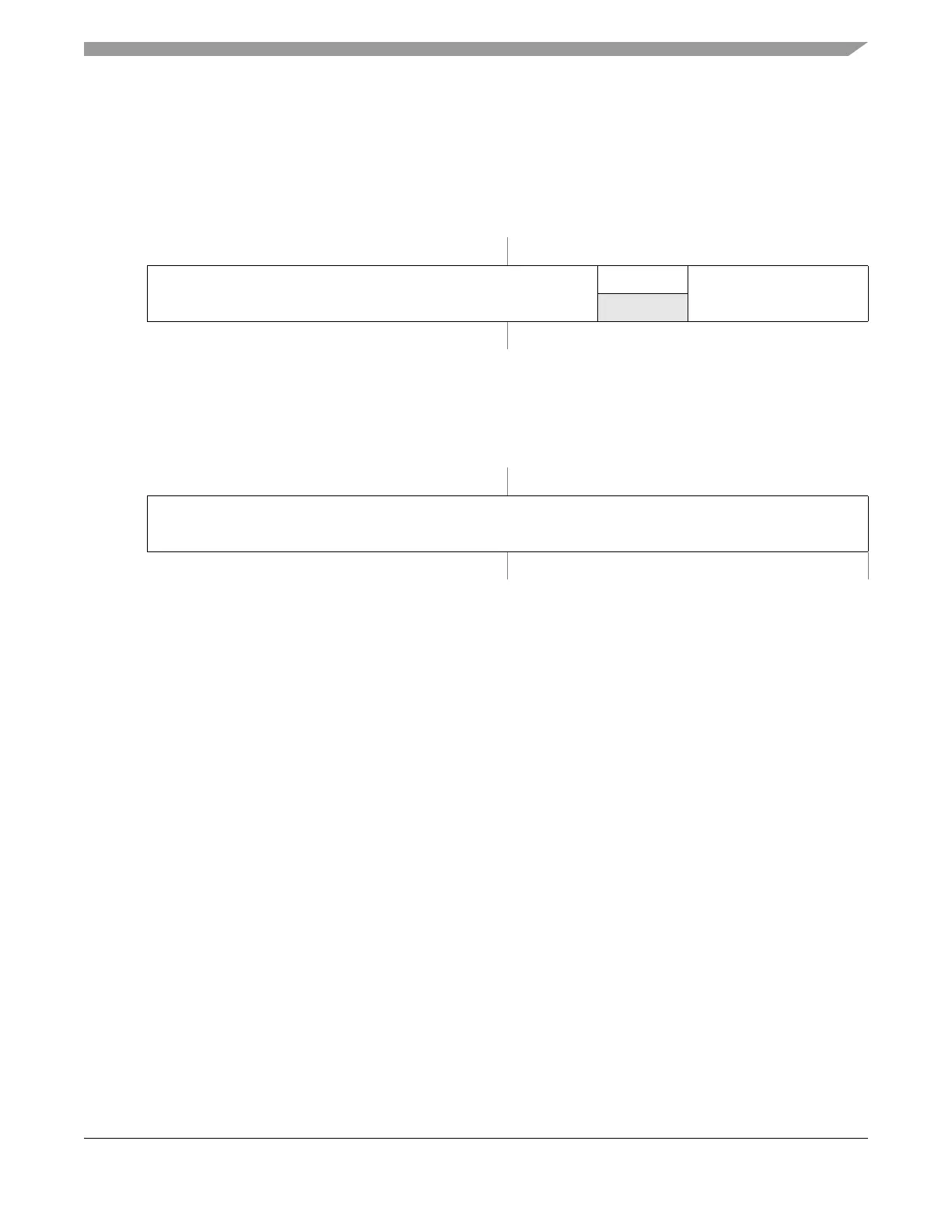

0x02F8

15 14 13 12 11 10 9 8

R

TCTRIM[4:0]

0

IRCTRIM[9:8]

W

Reset F F F F 0 0 F F

After de-assert of System Reset a factory programmed trim value is automatically loaded from the Flash memory to

provide trimmed Internal Reference Frequency f

IRC1M_TRIM

.

Figure 10-23. S12CPMU IRC1M Trim High Register (CPMUIRCTRIMH)

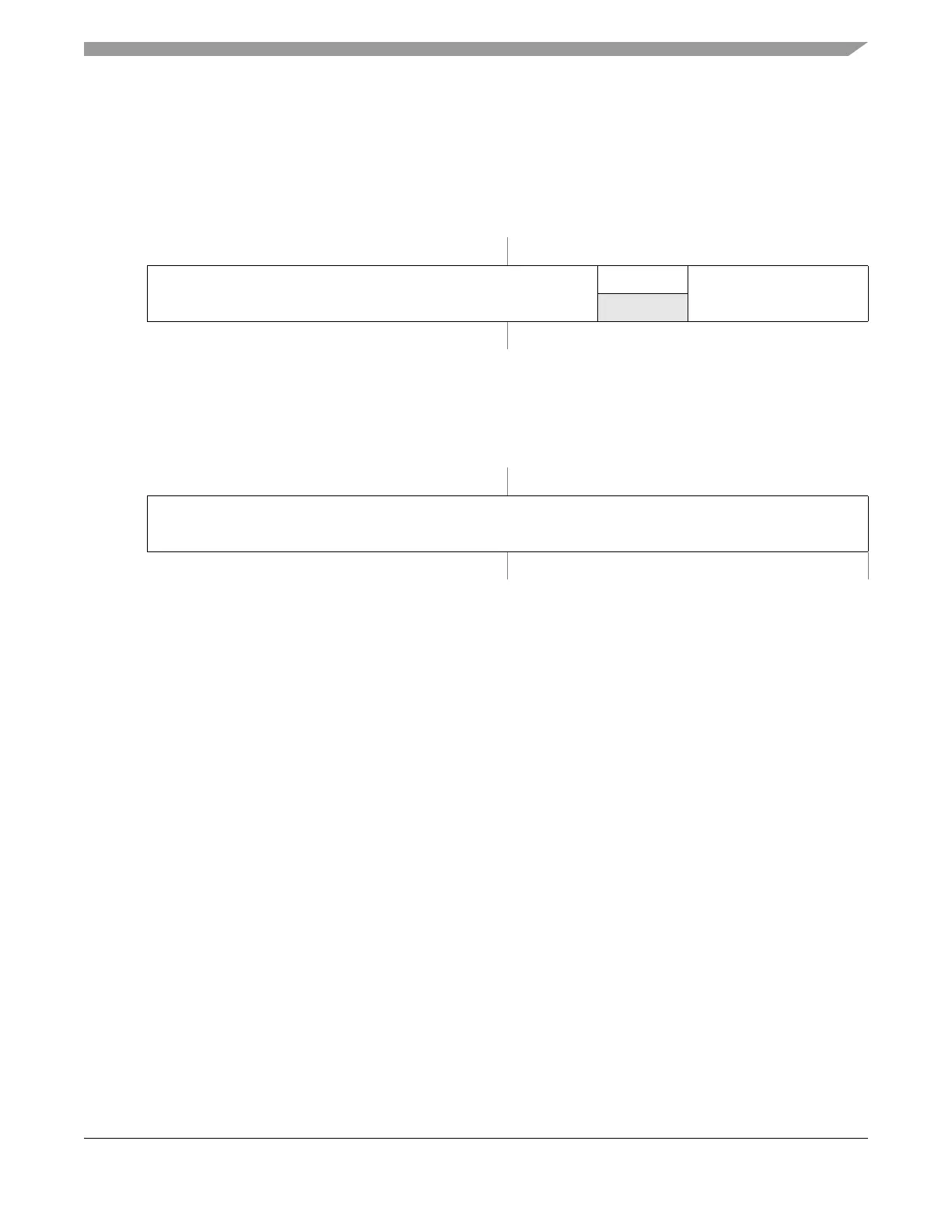

0x02F9

76543210

R

IRCTRIM[7:0]

W

ResetFFFFFFFF

After de-assert of System Reset a factory programmed trim value is automatically loaded from the Flash memory to

provide trimmed Internal Reference Frequency f

IRC1M_TRIM

.

Figure 10-24. S12CPMU IRC1M Trim Low Register (CPMUIRCTRIML)

Loading...

Loading...