Analog-to-Digital Converter (ADC10B12CV2)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 465

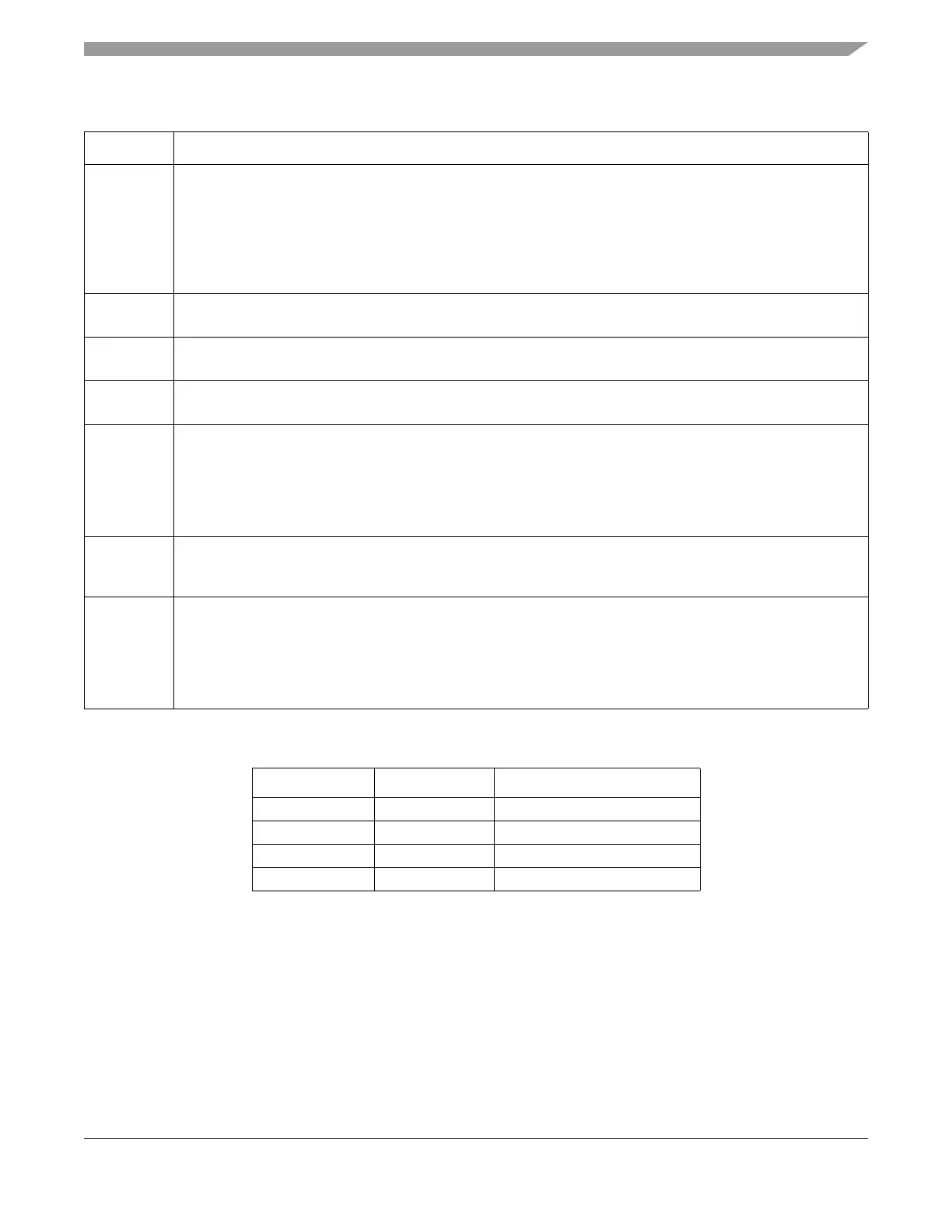

Table 13-6. ATDCTL2 Field Descriptions

Field Description

6

AFFC

ATD Fast Flag Clear All

0 ATD flag clearing done by write 1 to respective CCF[n] flag.

1 Changes all ATD conversion complete flags to a fast clear sequence.

For compare disabled (CMPE[n]=0) a read access to the result register will cause the associated CCF[n] flag

to clear automatically.

For compare enabled (CMPE[n]=1) a write access to the result register will cause the associated CCF[n] flag

to clear automatically.

5

Reserved

Do not alter this bit from its reset value.It is for Manufacturer use only and can change the ATD behavior.

4

ETRIGLE

External Trigger Level/Edge Control — This bit controls the sensitivity of the external trigger signal. See

Table 13-7 for details.

3

ETRIGP

External Trigger Polarity — This bit controls the polarity of the external trigger signal. See Table 13-7 for details.

2

ETRIGE

External Trigger Mode Enable — This bit enables the external trigger on one of the AD channels or one of the

ETRIG3-0 inputs as described in Table 13-5. If the external trigger source is one of the AD channels, the digital

input buffer of this channel is enabled. The external trigger allows to synchronize the start of conversion with

external events.

0 Disable external trigger

1 Enable external trigger

1

ASCIE

ATD Sequence Complete Interrupt Enable

0 ATD Sequence Complete interrupt requests are disabled.

1 ATD Sequence Complete interrupt will be requested whenever SCF=1 is set.

0

ACMPIE

ATD Compare Interrupt Enable — If automatic compare is enabled for conversion n (CMPE[n]=1 in ATDCMPE

register) this bit enables the compare interrupt. If the CCF[n] flag is set (showing a successful compare for

conversion n), the compare interrupt is triggered.

0 ATD Compare interrupt requests are disabled.

1 For the conversions in a sequence for which automatic compare is enabled (CMPE[n]=1), an ATD Compare

Interrupt will be requested whenever any of the respective CCF flags is set.

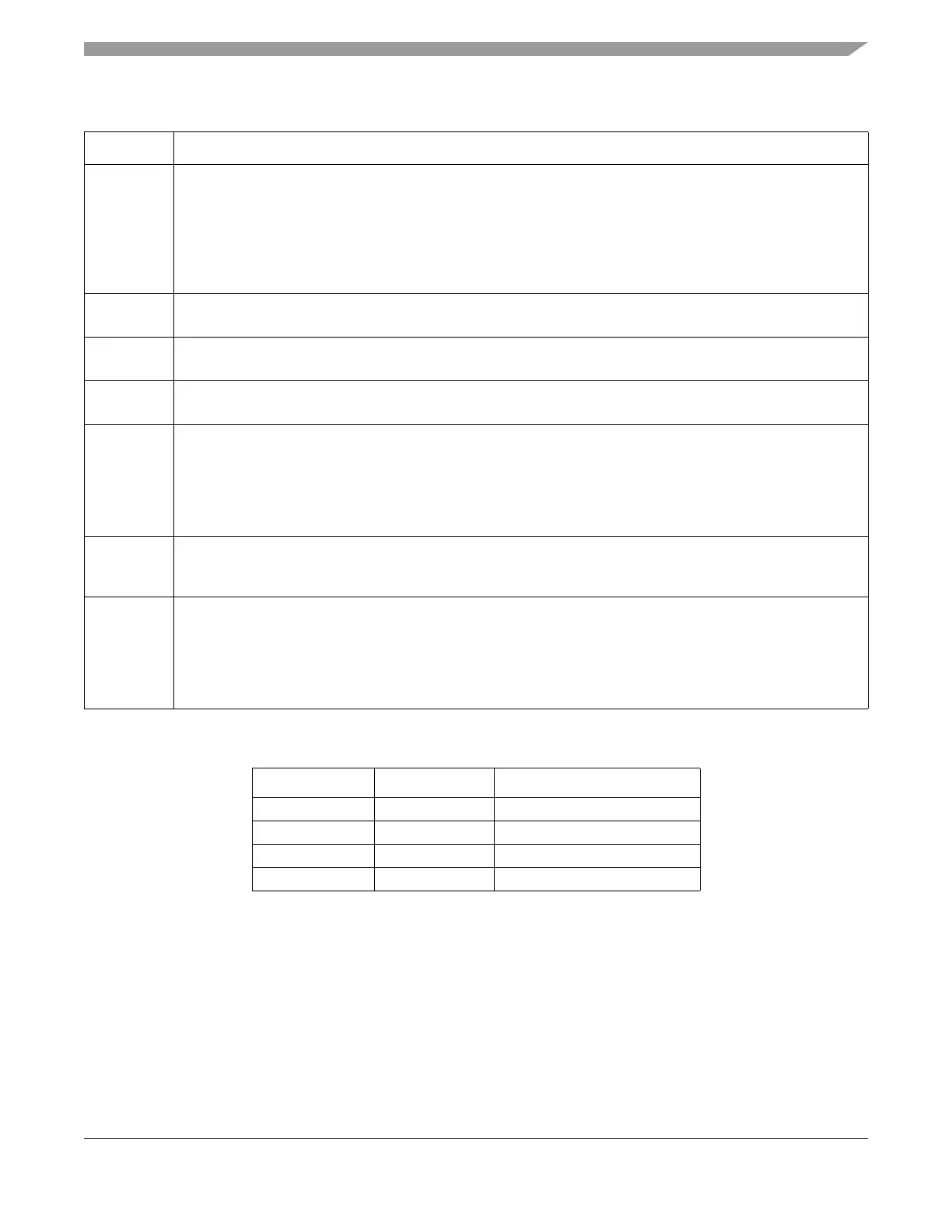

Table 13-7. External Trigger Configurations

ETRIGLE ETRIGP External Trigger Sensitivity

0 0 Falling edge

0 1 Rising edge

1 0 Low level

1 1 High level

Loading...

Loading...