Serial Communication Interface (S12SCIV5)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 675

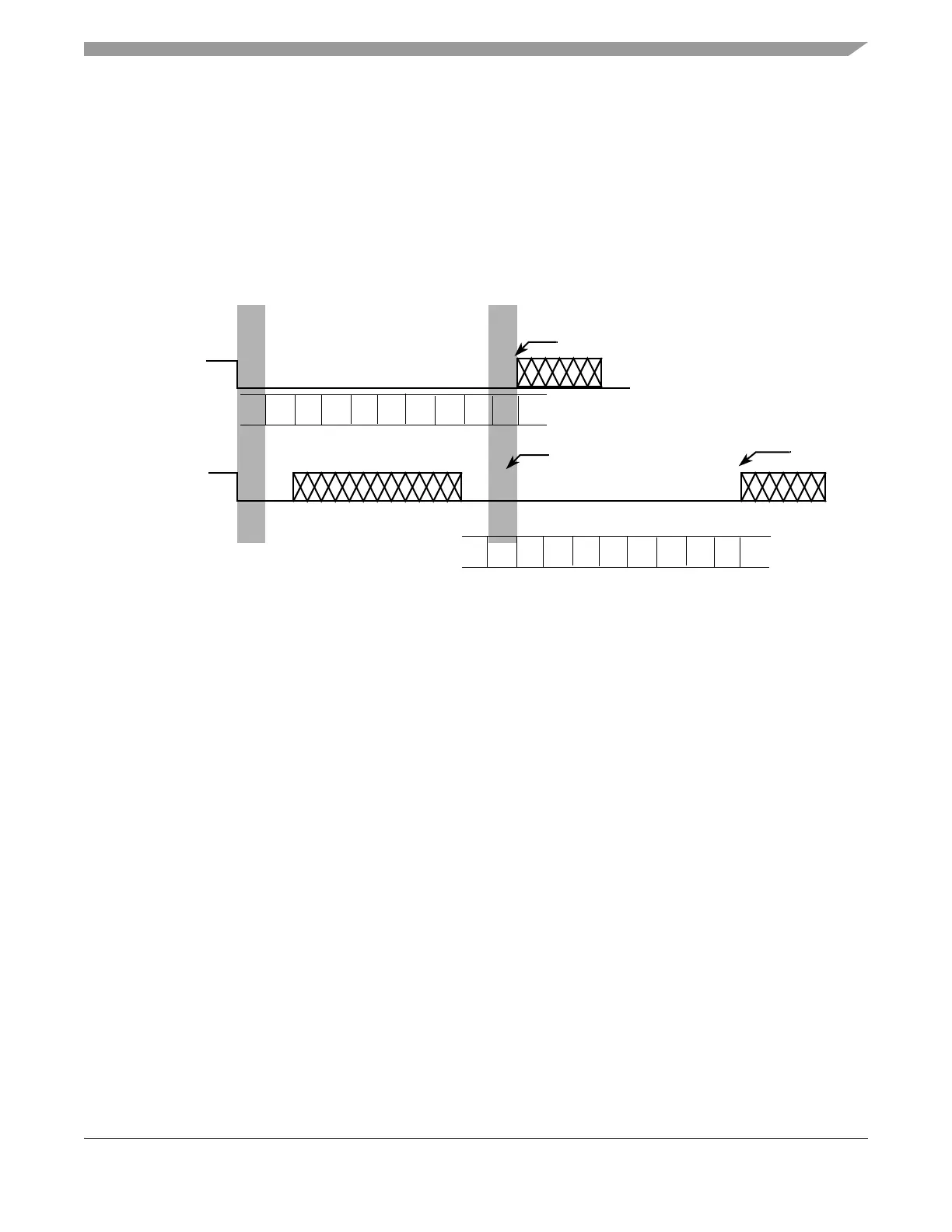

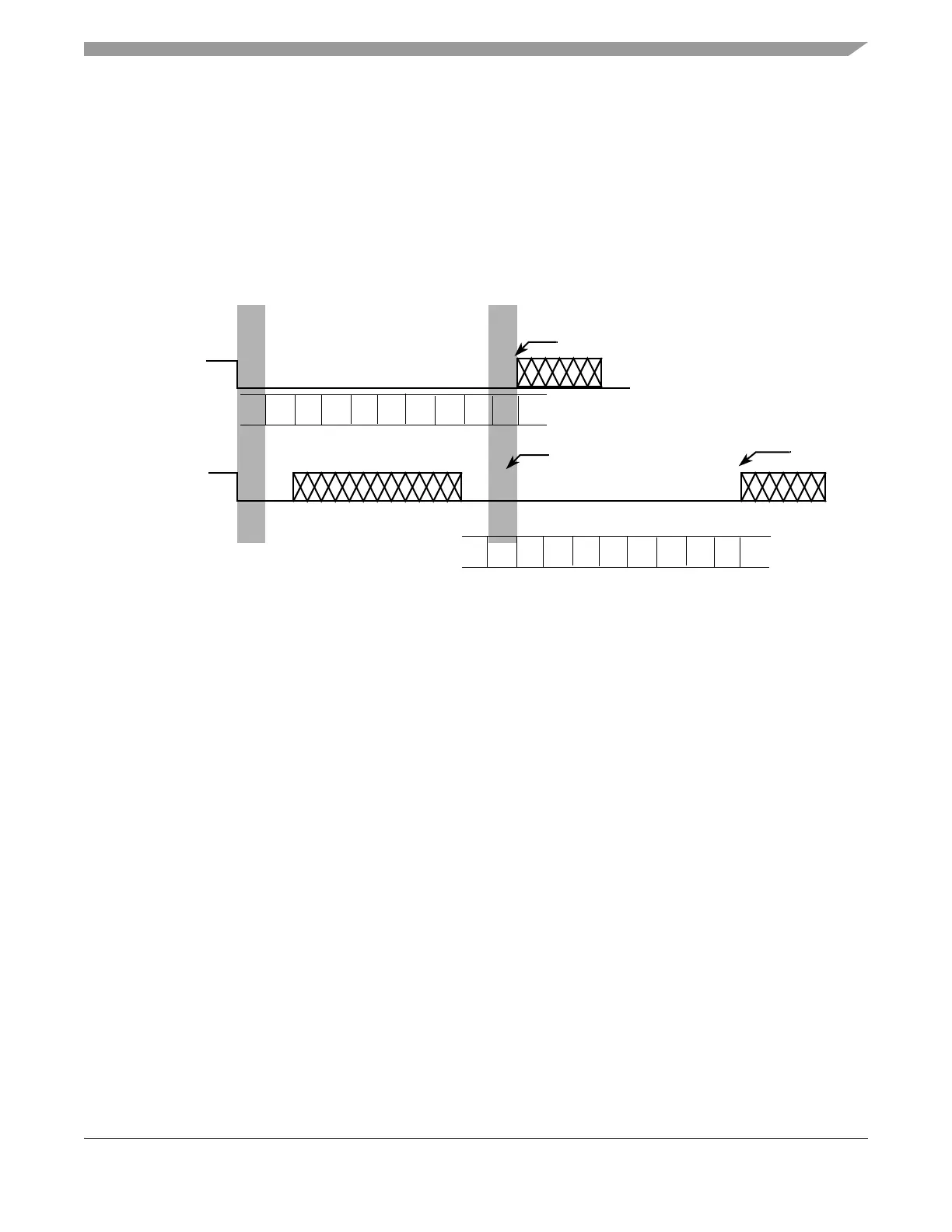

Figure 20-17 shows two cases of break detect. In trace RXD_1 the break symbol starts with the start bit,

while in RXD_2 the break starts in the middle of a transmission. If BRKDFE = 1, in RXD_1 case there

will be no byte transferred to the receive buffer and the RDRF flag will not be modified. Also no framing

error or parity error will be flagged from this transfer. In RXD_2 case, however the break signal starts later

during the transmission. At the expected stop bit position the byte received so far will be transferred to the

receive buffer, the receive data register full flag will be set, a framing error and if enabled and appropriate

a parity error will be set. Once the break is detected the BRKDIF flag will be set.

Figure 20-17. Break Detection if BRKDFE = 1 (M = 0)

20.4.5.4 Idle Characters

An idle character (or preamble) contains all logic 1s and has no start, stop, or parity bit. Idle character

length depends on the M bit in SCI control register 1 (SCICR1). The preamble is a synchronizing idle

character that begins the first transmission initiated after writing the TE bit from 0 to 1.

If the TE bit is cleared during a transmission, the TXD pin becomes idle after completion of the

transmission in progress. Clearing and then setting the TE bit during a transmission queues an idle

character to be sent after the frame currently being transmitted.

NOTE

When queueing an idle character, return the TE bit to logic 1 before the stop

bit of the current frame shifts out through the TXD pin. Setting TE after the

stop bit appears on TXD causes data previously written to the SCI data

register to be lost. Toggle the TE bit for a queued idle character while the

TDRE flag is set and immediately before writing the next byte to the SCI

data register.

If the TE bit is clear and the transmission is complete, the SCI is not the

master of the TXD pin

Start Bit Position Stop Bit Position

BRKDIF = 1

FE = 1

BRKDIF = 1

RXD_1

RXD_2

123 4567 8 910

123 4567 8 910

Zero Bit Counter

Zero Bit Counter

. . .

. . .

Loading...

Loading...