Timer Module (TIM16B6CV3)

MC9S12G Family Reference Manual Rev.1.27

732 NXP Semiconductors

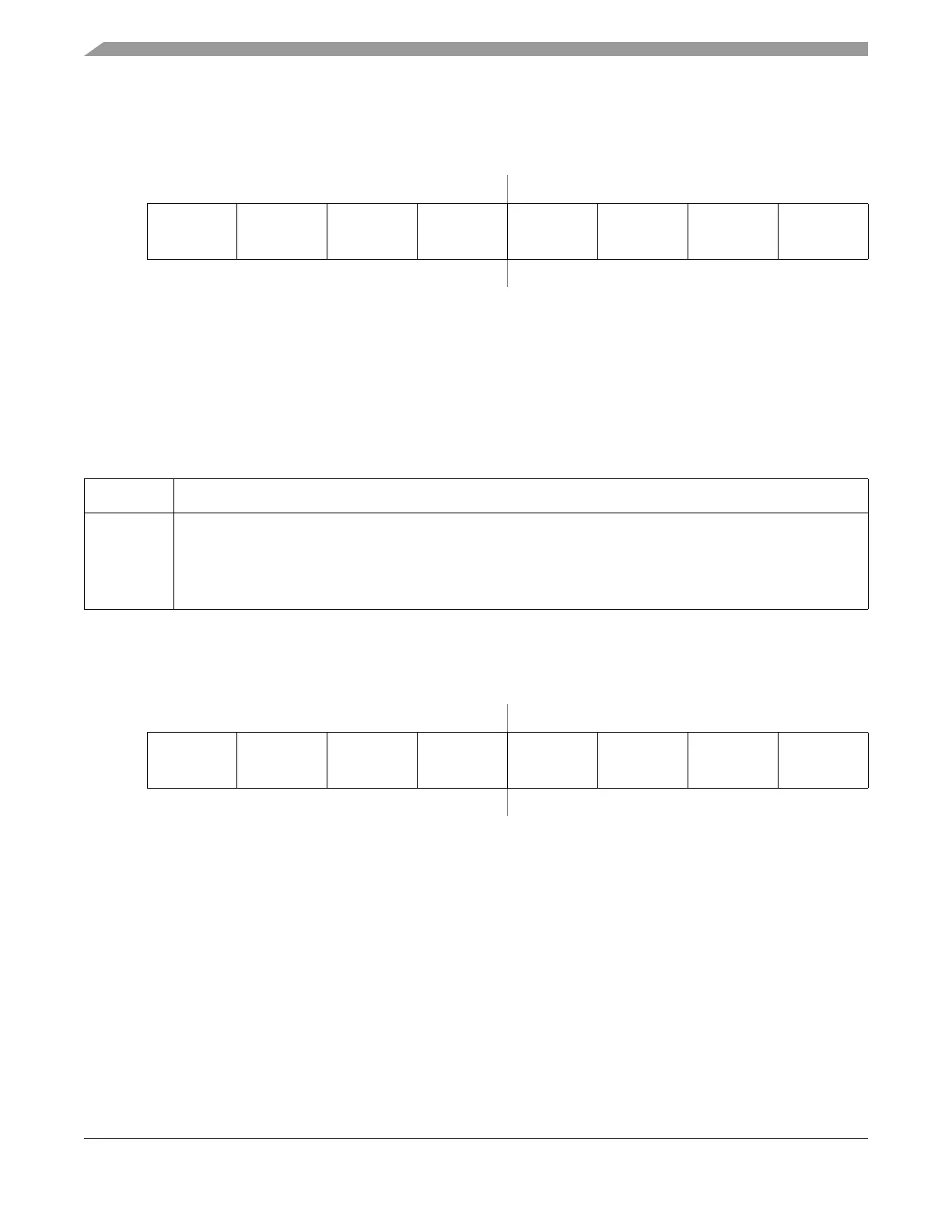

22.3.2.13 Output Compare Pin Disconnect Register(OCPD)

Read: Anytime

Write: Anytime

All bits reset to zero.

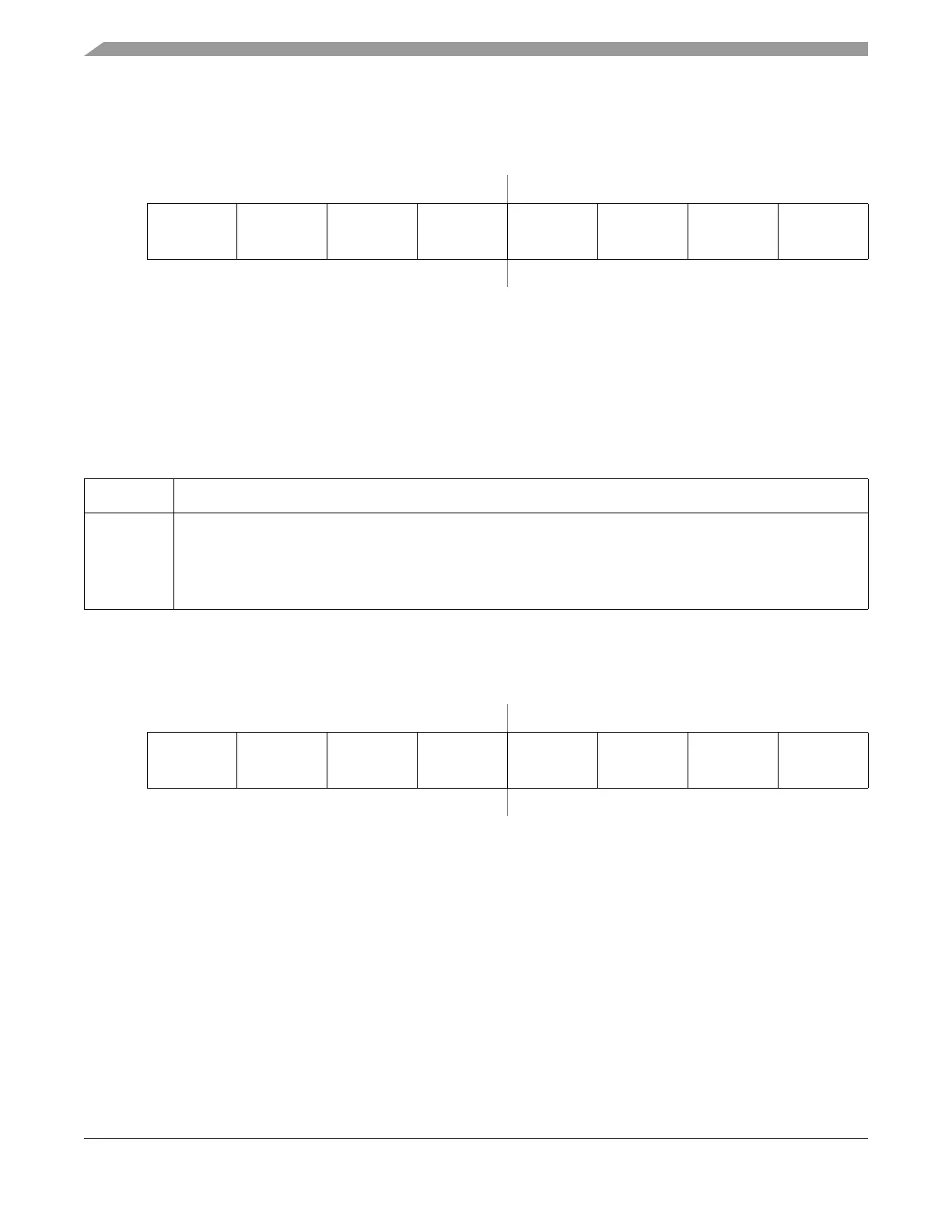

22.3.2.14 Precision Timer Prescaler Select Register (PTPSR)

Read: Anytime

Write: Anytime

All bits reset to zero.

Module Base + 0x002C

76543210

R

RESERVED RESERVED OCPD5 OCPD4 OCPD3 OCPD2 OCPD1 OCPD0

W

Reset00000000

Figure 22-20. Output Compare Pin Disconnect Register (OCPD)

Table 22-15. OCPD Field Description

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

Field Description

5:0

OCPD[5:0]

Output Compare Pin Disconnect Bits

0 Enables the timer channel port. Output Compare action will occur on the channel pin. These bits do not affect

the input capture .

1 Disables the timer channel port. Output Compare action will not occur on the channel pin, but the output

compare flag still become set.

Module Base + 0x002E

76543210

R

PTPS7 PTPS6 PTPS5 PTPS4 PTPS3 PTPS2 PTPS1 PTPS0

W

Reset00000000

Figure 22-21. Precision Timer Prescaler Select Register (PTPSR)

Loading...

Loading...