RL78/G15 CHAPTER 4 PORT FUNCTIONS

R01UH0959EJ0110 Rev.1.10 Page 120 of 765

Mar 7, 2023

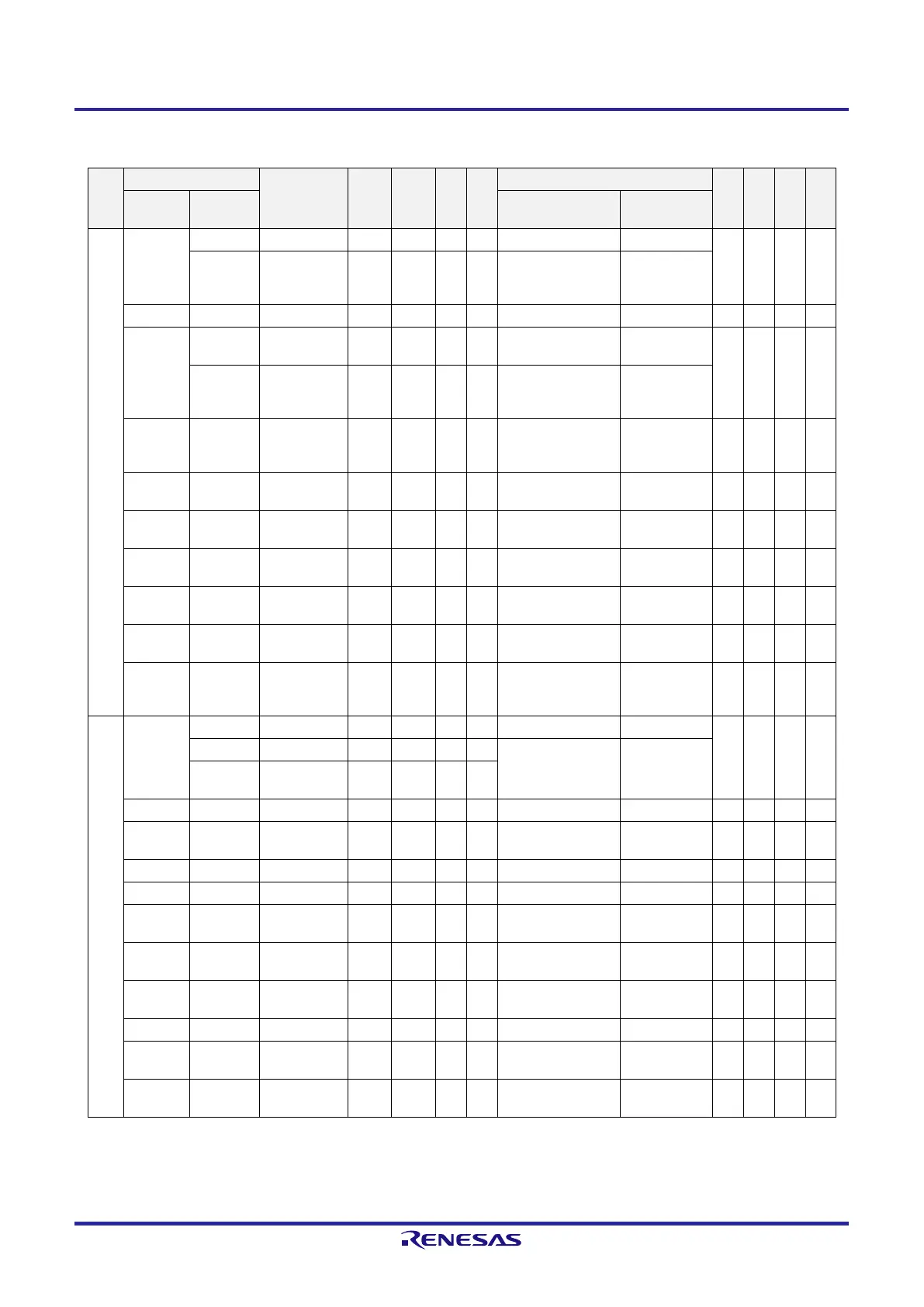

Table 4-7. Setting Examples of Registers and Output Latches When Using Pin Function (3/10)

Pin

Name

Used Function PIORr POMp PMCq PMn Pm Alternate Function Output 20-

pin

16-

pin

10-

pin

8-

pin

Function

Name

I/O SAU Output Function Other than SAU

P02 P02 Input — — 0 1 × × × —

Output — — 0 0 0/1 SCK00/SCL00 = 1

(SO01) = 1

Note 1

PCLBUZ0 = 0

VCOUT0 = 0

(TO01) = 0

ANI1 Analog input — — 1 1 × × × —

SCK00 Input PIOR11 = 0

Note 1

PIOR10 = 0

Note 1

— 0 1 × × × —

Output PIOR11 = 0

Note 1

PIOR10 = 0

Note 1

— 0 0 1 (SO01) = 1

Note 1

PCLBUZ0 = 0

VCOUT0 = 0

(TO01) = 0

SCL00 Output PIOR11 = 0

Note 1

PIOR10 = 0

Note 1

— 0 0 1 (SO01) = 1

Note 1

PCLBUZ0 = 0

VCOUT0 = 0

(TO01) = 0

—

PCLBUZ0 Output PIOR31 = 0

Note 1

PIOR30 = 0

— 0 0 0 × VCOUT0 = 0

(TO01) = 0

—

VCOUT0 Output PIOR32 = 0 — 0 0 0 × PCLBUZ0 = 0

(TO01) = 0

—

INTP7 Input PIOR35 = 0

Note 2

PIOR34 = 0

Note 1

— 0 1 × × × —

(TI01) Input PIOR03 = 1

PIOR02 = 0

— 0 1 × × × —

(TO01) Output PIOR03 = 1

PIOR02 = 0

— 0 0 0 × PCLBUZ0 = 0

VCOUT0 = 0

—

(SO01) Output PIOR13 = 0

Note 2

PIOR12 = 1

— 0 0 1 SCK00/SCL00 = 1 PCLBUZ0 = 0

VCOUT0 = 0

(TO01) = 0

— —

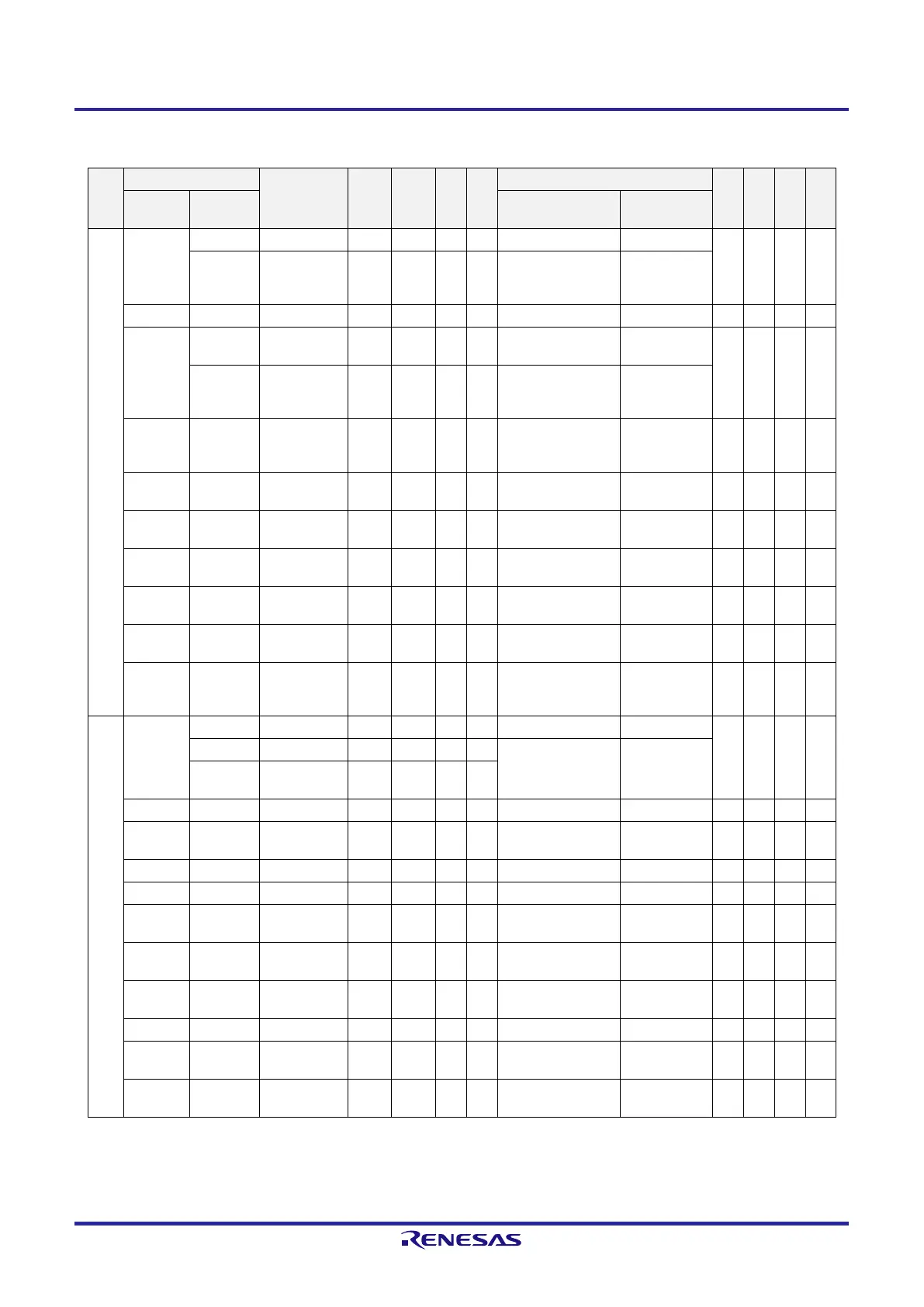

P03 P03 Input — × 0 1 × × ×

Output — 0 0 0 0/1 SO00/TxD0 = 1

Note 4

(SO00/TxD0) = 1

Note 1

TO00 = 0

SCLA0 = 0

Note 3

N-ch open

drain output

— 1 0 0 0/1

ANI2 Analog input — × 1 1 × × ×

TO00 Output PIOR01 = 0

Note 2

PIOR00 = 0

Note 2

0 0 0 0 × SCLA0 = 0

Note 3

INTP4 Input PIOR23 = 0

Note 1

× 0 1 × × ×

IVCMP0 Input — × 1 1 × × ×

(TI00) Input PIOR01 = 0

Note 2

PIOR00 = 1

× 0 1 × × ×

(SO00) Output PIOR11 = 1

PIOR10 = 0

0 0 0 1 × TO00 = 0 — —

(TxD0) Output PIOR11 = 1

PIOR10 = 0

0/1 0 0 1 × TO00 = 0 — —

SCLA0 I/O — 1 0 0 0 × TO00 = 0 — —

SO00 Output — 0 0 0 1 × TO00 = 0

SCLA0 = 0

— — —

TxD0 Output — 0/1 0 0 1 × TO00 = 0

SCLA0 = 0

— — —

Loading...

Loading...