RL78/G15 CHAPTER 6 TIMER ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 172 of 765

Mar 7, 2023

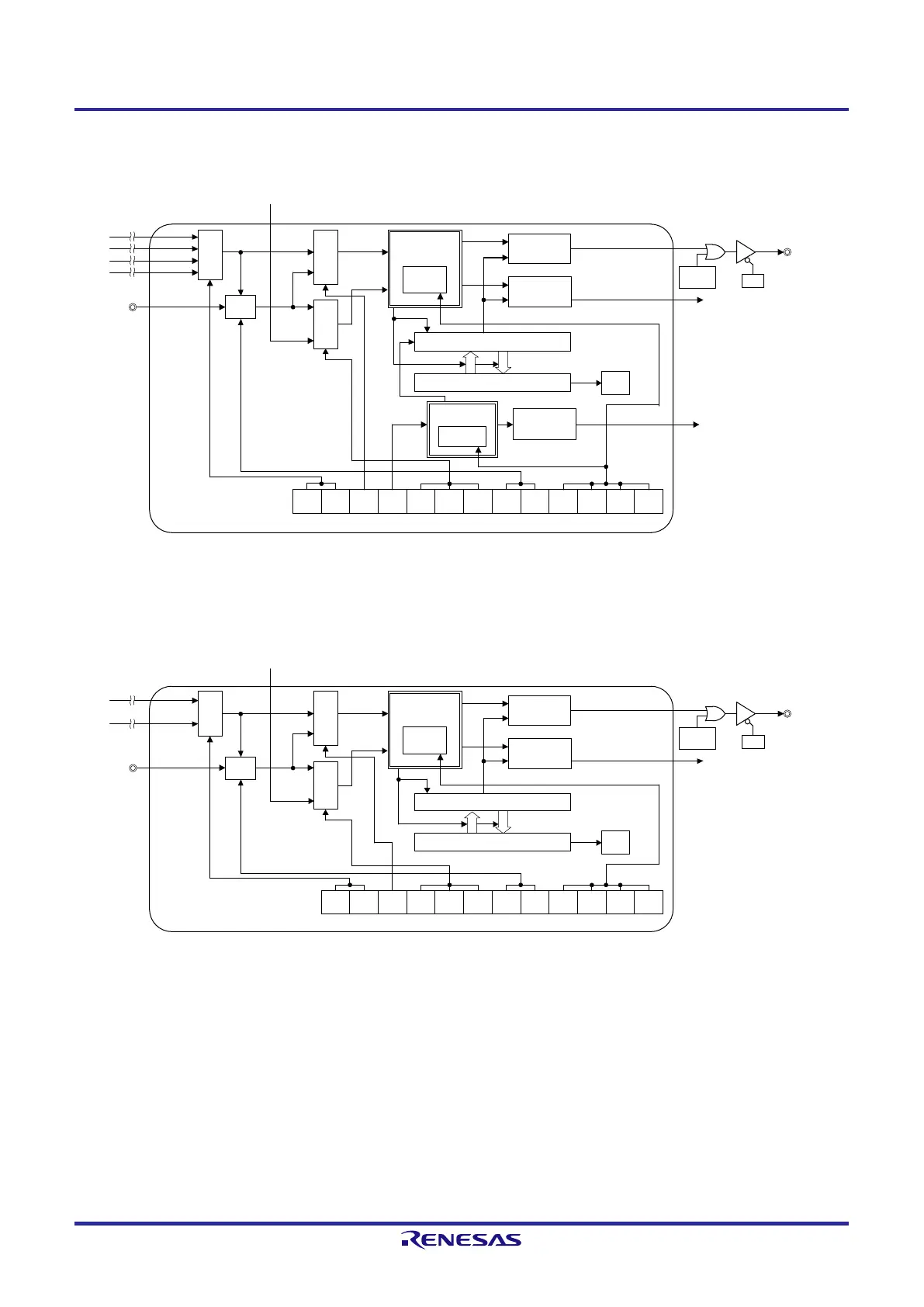

Figure 6-4. Internal Block Diagram of Channel 3 of Timer Array Unit

Timer controller

Mode

selection

f

MCK

Edge

detection

Output

controller

Output latch

(Pxx

)

OVF

0n

CK00

CK01

Timer counter register

0

n (

TCR

0

n

)

Timer data register

0n (TDR0n)

CK02

CK03

Interrupt

controller

INTTM

0nH

(

Timer interrupt)

Input signal from the master channel

Overflow

Timer status register

0

n (

TSR

0n

)

INTTM0

n

(Timer interrupt

)

Channel n

Timer mode register 0

n (TMR

0n)

CKS

0n

1

CKS0

n0

CCS

0n

SPLIT

0

n

STS0n2 STS0n1 STS0n0 CIS0n1 CIS0n0 MD

0n

3 MD

0

n2

MD

0n

1 MD

0

n0

Operation

clock

selection

Count clock

selection

TI0

n

f

TCLK

Interrupt

controller

8-bit timer

controller

Mode

selection

TO

0n

PMxx

Trigger

selection

Remark n = 3

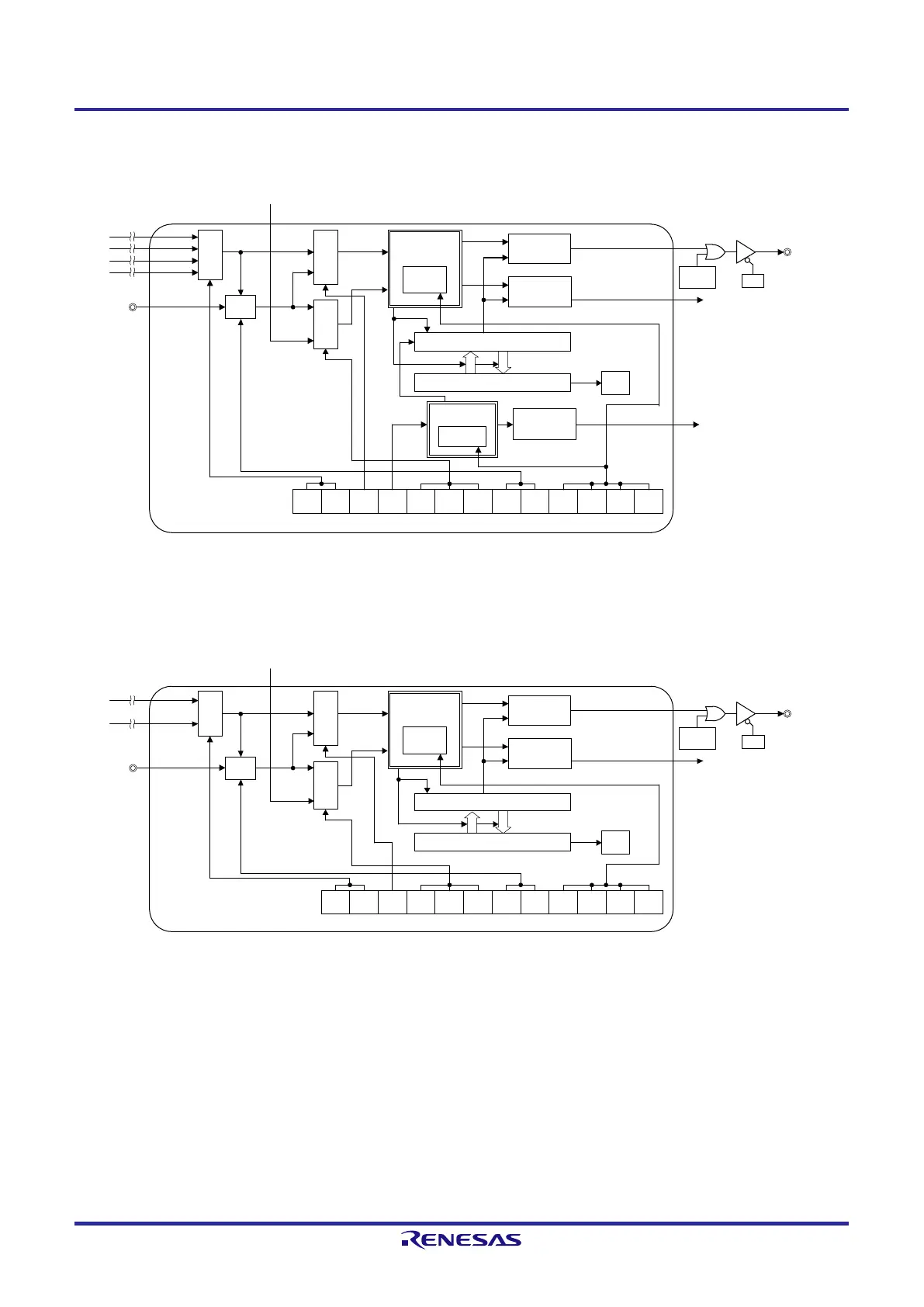

Figure 6-5. Internal Block Diagram of Channel n (n = 5, 7) of Timer Array Unit

CKS0n1

Timer controller

Edge

detection

Mode

selection

Interrupt

controller

Output

controller

OVF

0n

CK00

CK01

TI0n

f

MCK

Timer counter register

0n (

TCR0n

)

Timer data register 0n (TDR0n)

Output latch

(

Pxx)

TO0n

INTTM0n

(Timer interrupt)

f

TCLK

Timer mode register 0n

(TMR0n)

Overflow

Timer status register

0n (TSR0n)

Input signal from the master channel

Operation

clock

selection

Count clock

selection

Channel n

CKS0n0

CCS0n

STS0n2

STS0n1

STS0n0

CIS0n1

CIS0n0

MD0n3

MD0n2

MD0n1

MD0n0

PMxx

Trigger

selection

Remark n = 5, 7

Loading...

Loading...