RL78/G15 CHAPTER 6 TIMER ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 217 of 765

Mar 7, 2023

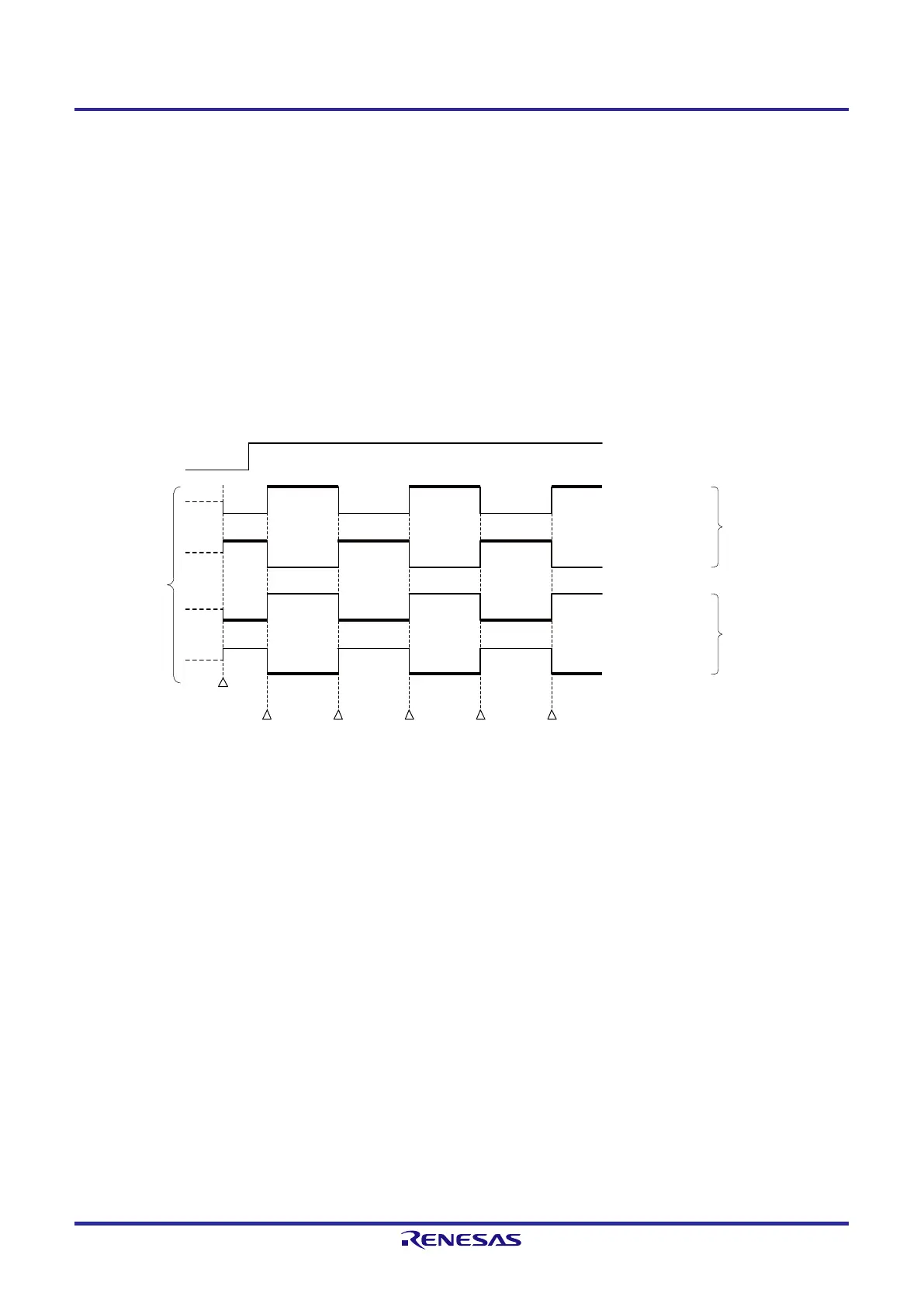

(2) Default level of TOmn pin and output level after timer operation start

The change in the output level of the TOmn pin when timer output register m (TOm) is written while timer output is

disabled (TOEmn = 0), the initial level is changed, and then timer output is enabled (TOEmn = 1) before port output is

enabled, is shown below.

(a) When operation starts with master channel output mode (TOMmn = 0) setting

The setting of timer output level register m (TOLm) is invalid when master channel output mode (TOMmn = 0). When the

timer operation starts after setting the default level, the toggle signal is generated and the output level of the TOmn pin is

reversed.

Figure 6-31. TOmn Pin Output Status at Toggle Output (TOMmn = 0)

Hi-Z

Default

status

TOEmn

Port

output is

enabled

Toggle Toggle Toggle Toggle Toggle

Bold

:

Active level

TOmn bit = 0

(Default status: Low)

TOmn bit

= 1

(Default status:

High)

TOmn bit = 0

(Default status: Low)

TOmn bit

= 1

(Default status: High)

TOmn

(Output)

TOLmn bit = 0

(Active high

)

TOLmn bit = 1

(Active low)

Remark 1. Toggle: Reverse TOmn pin output status

Remark 2. m: Unit number (m = 0), n: Channel number (n = 0 to 7)

Loading...

Loading...