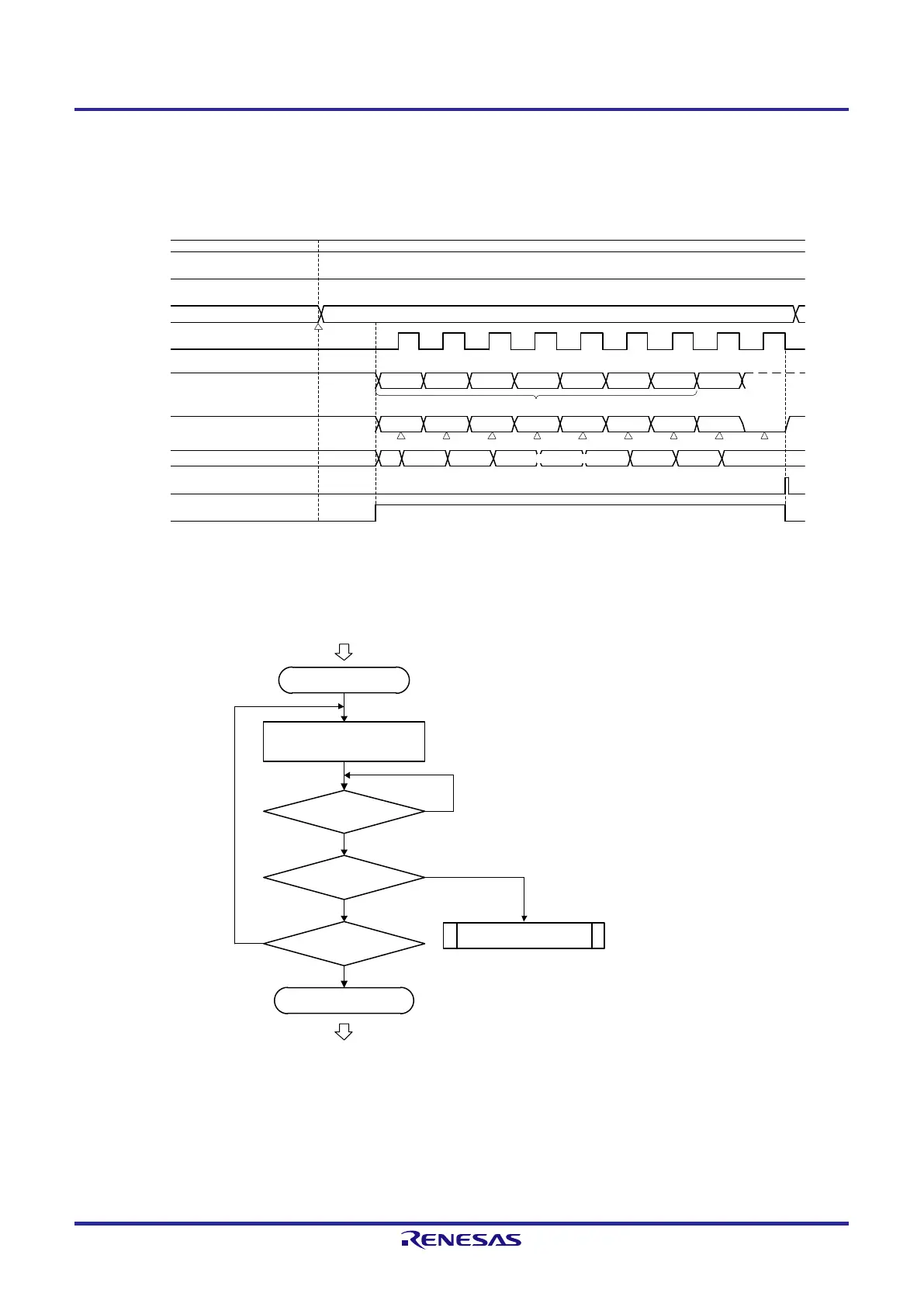

Writing data to

SIOr (SDRmn[7:0])

Data transfer completed?

Yes

Stop condition generation

Communication error

processing

Responded ACK?

No

ACK acknowledgment from the slave

If ACK (PEF = 0), to the next process

if NACK (PEF = 1), to error handling

No

Yes

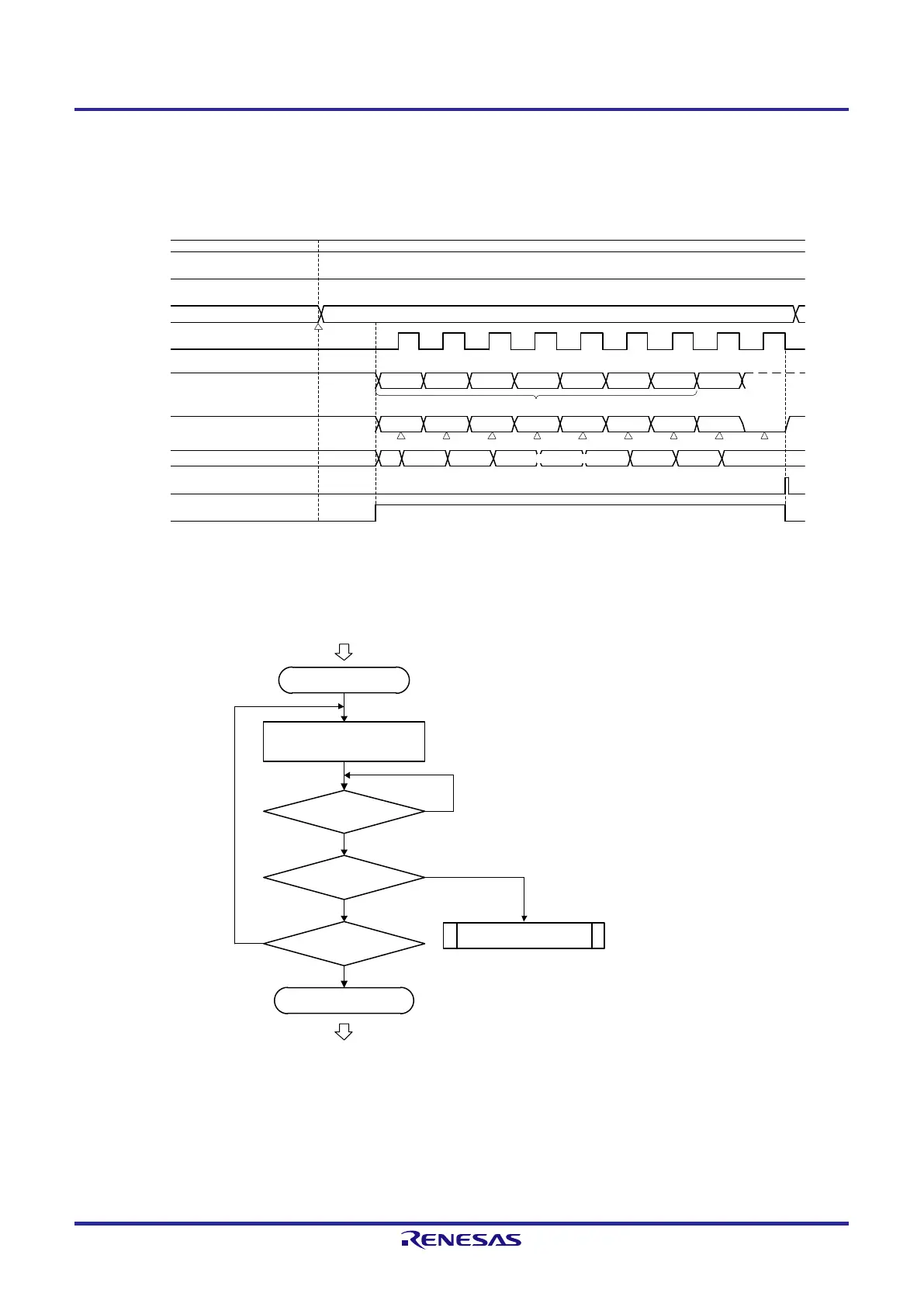

Transmission start by writing

Data transmission completed

Transfer end interrupt

generated?

Yes

Starting data transmission

No

Wait for transmission complete.

(Clear the interrupt request flag)

Address field transmission

completed

Loading...

Loading...