RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 546 of 765

Mar 7, 2023

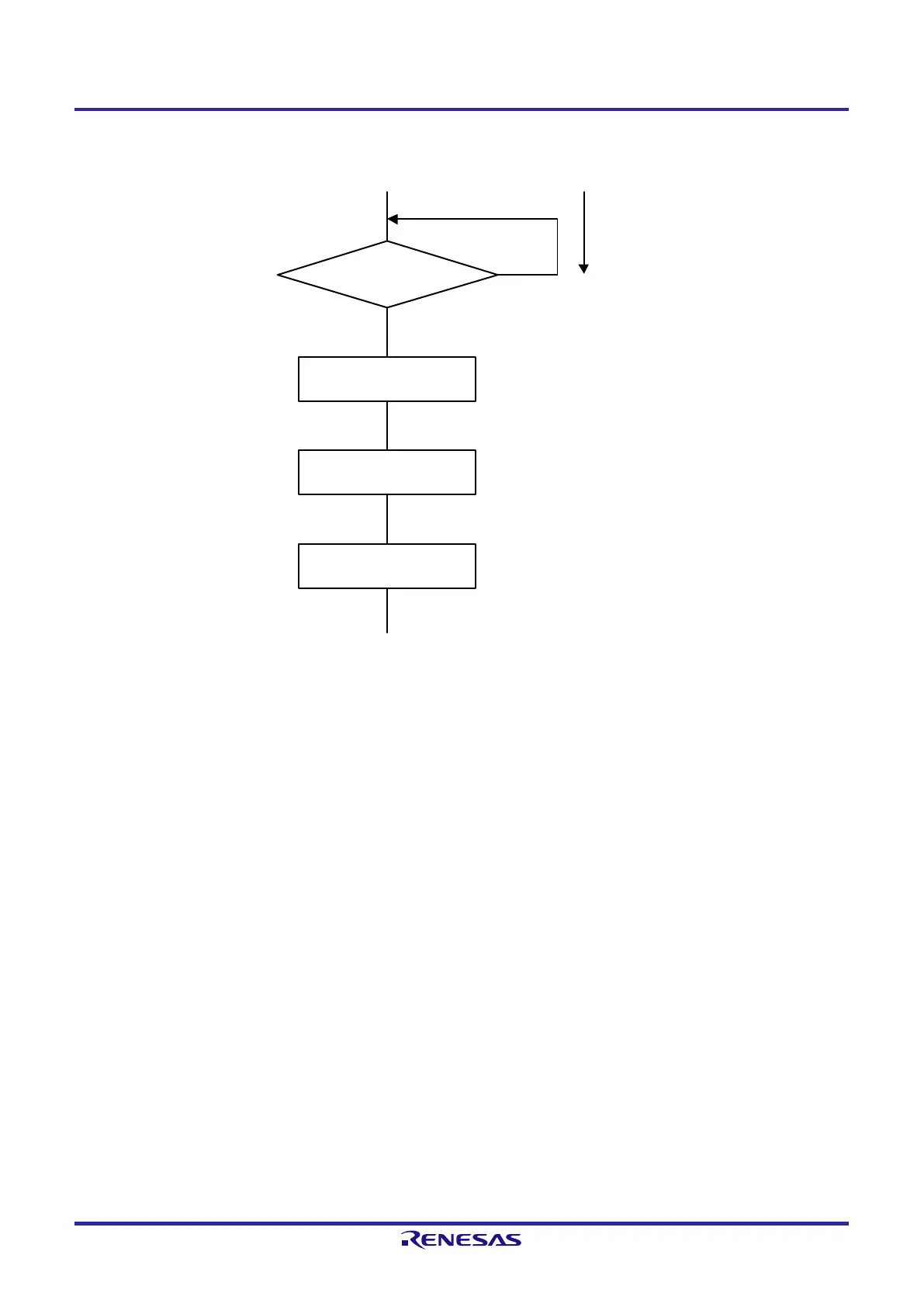

Figure 13-22. Flow when Setting WUP0 = 0 upon Address Match (Including Extension Code Reception)

Yes

No

Wait for 5 clock cycles of f

CLK

INTIICA

0

= 1

?

WUP0 = 0

Wait

Read IICS0

In STOP mode

After checking the operation state of serial interface

IICA, execute processing corresponding to

the operation to execute

.

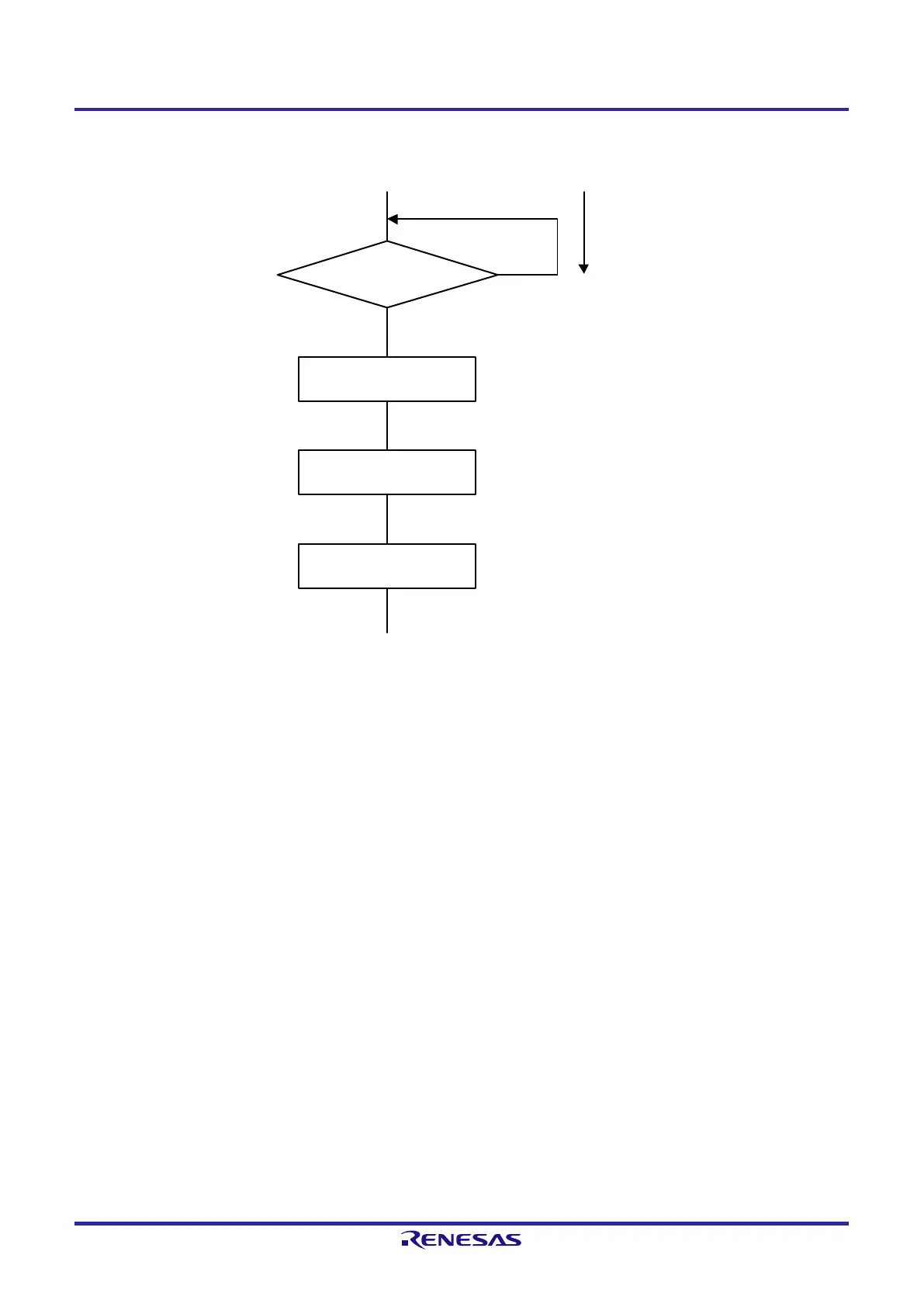

Follow the flow below to perform the processing to release the STOP mode other than by an interrupt request signal

(INTIICA0) from serial interface IICA.

●

When operating next I

2

C communication as a master:

—

Flow shown in Figure 13-23

●

When operating next I

2

C communication as a slave:

—

When recovered by the INTIICA0 interrupt: Same as the flow in Figure 13-22.

—

When recovered by an interrupt other than the INTIICA0 interrupt:

Continue operation with WUP0 set to 1 until the INTIICA0 interrupt is generated.

Loading...

Loading...