RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 590 of 765

Mar 7, 2023

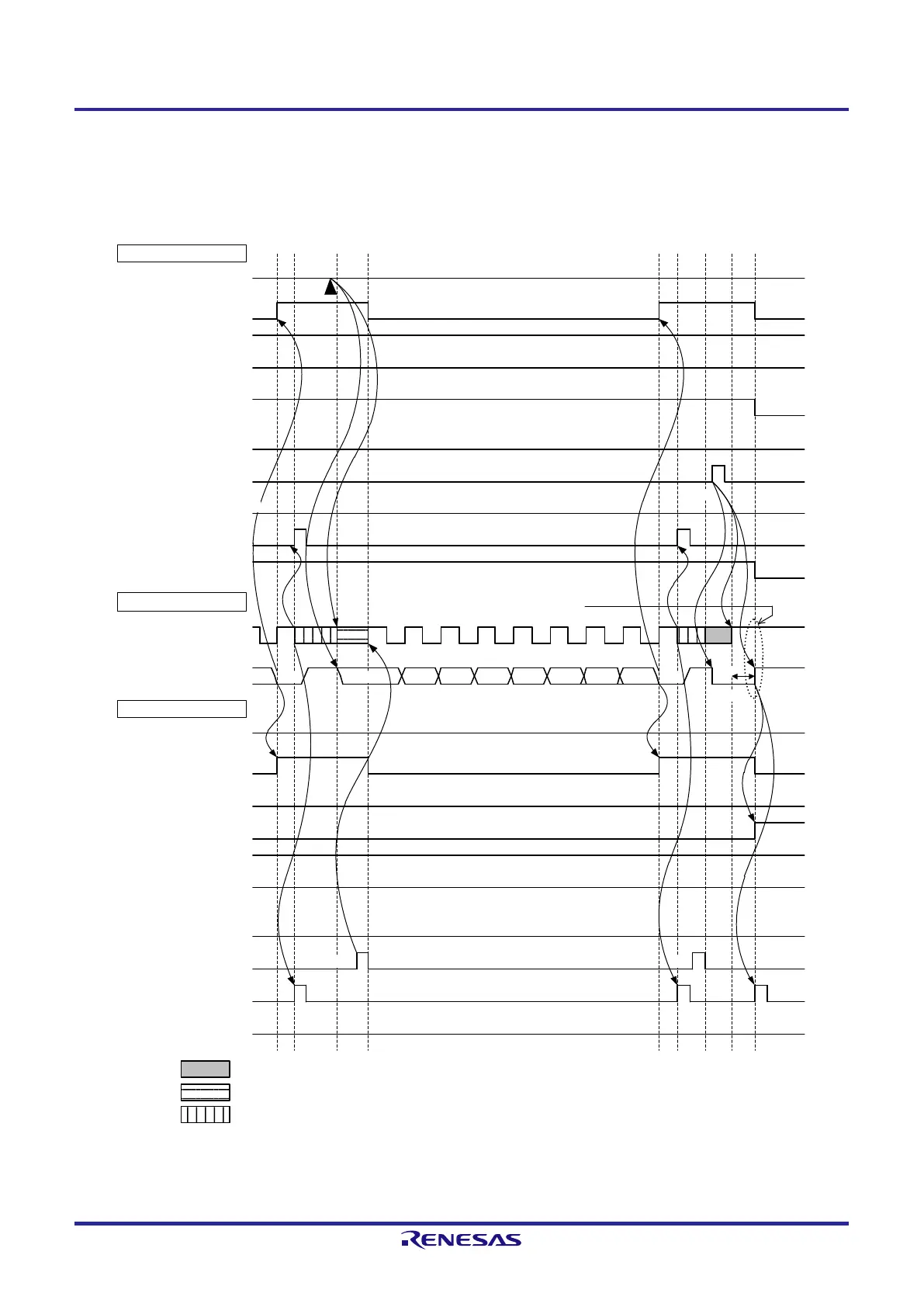

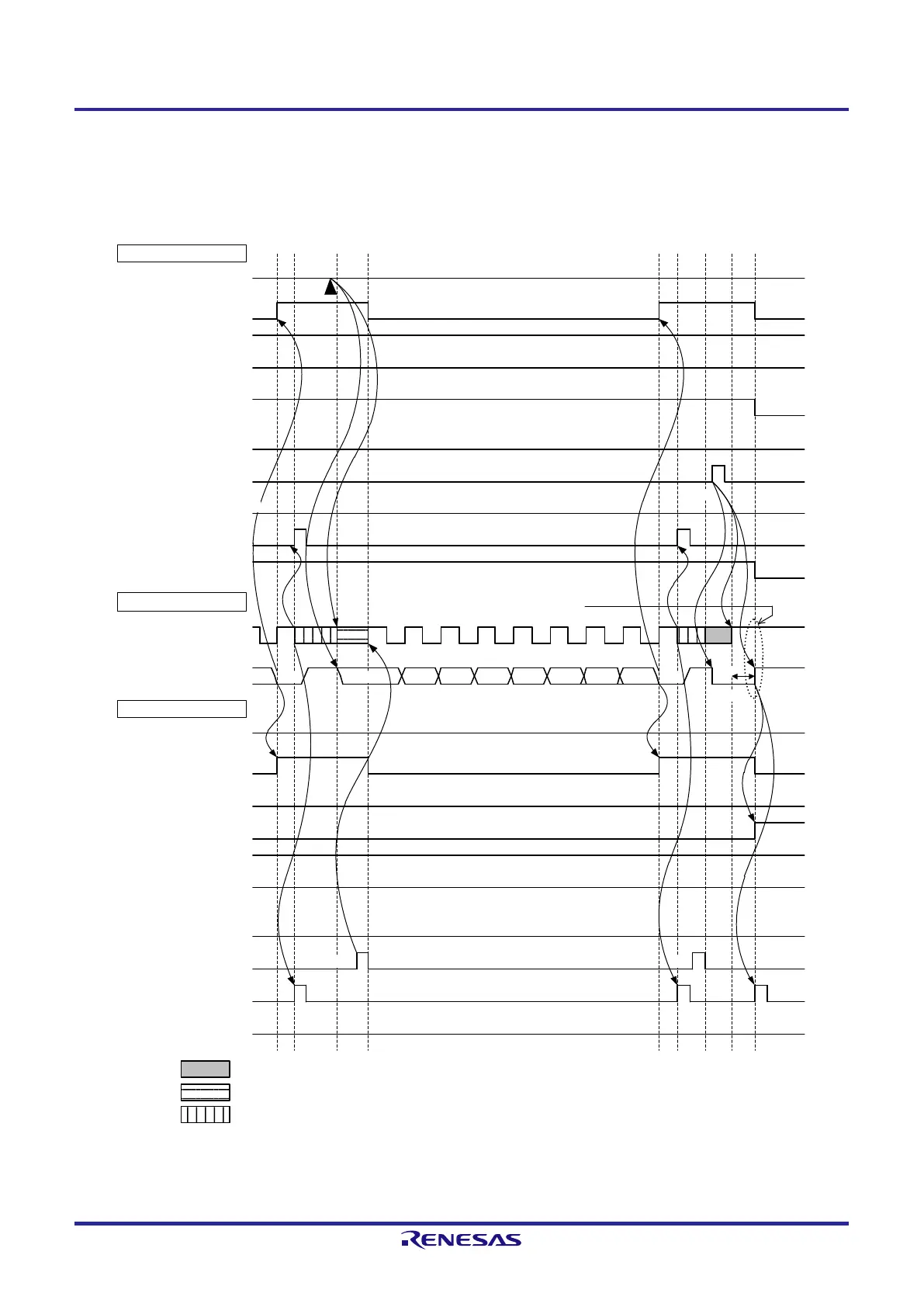

Figure 13-31. Example of Master to Slave Communications

(9th Cycle Clock Stretching is Selected for Both Master and Slave) (3/4)

(3) Data ~ data ~ stop condition

IICA0

ACKD0

(ACK detection)

<9>

H

H

D

16

6 D

16

5

Master side

STT0

(ST trigger)

SPT0

(SP trigger)

WREL0

(release clock stretching)

INTIICA0

(interrupt)

TRC0

(transmission/reception)

Bus line

SCLA0 (bus)

(clock line)

SDAA0 (bus)

(data line)

D

16

7 D

16

4 D

16

3 D

16

2 D

16

1

Slave side

IICA0

ACKD0

(ACK detection)

<11>

<12>

H

H

L

L

<13>

Note 3

STD0

(ST detection)

SPD0

(SP detection)

WTIM0

(Clock stretch timing control)

ACKE0

(ACK control)

MSTS0

(communication state)

WREL0

(release clock stretching)

INTIICA0

(interrupt)

TRC0

(transmission/reception)

WTIM0

(Clock stretch timing control)

ACKE

0

(ACK control

)

MSTS0

(communication state)

D

16

0

Note 1

L

<8

>

<7>

L

Note 3

<10>

L

D

15

0 ACK ACK

<15

>

Stop condition

Note 2

<14>

: Clock stretching by the master

: Clock stretching by the slave

: Clock stretching by the master and slave

Note 1. To release clock stretching in transmission by the master, write data to the IICA0 register instead of setting

the WREL0 bit.

Loading...

Loading...