RL78/G15 CHAPTER 3 CPU ARCHITECTURE

R01UH0959EJ0110 Rev.1.10 Page 60 of 765

Mar 7, 2023

The internal program memory space is divided into the following areas.

(1) Vector table area

The 128-byte area 00000H to 0007FH is reserved as a vector table area. The program start addresses for branch upon

reset or generation of each interrupt request are stored in the vector table area. Furthermore, the interrupt jump address

is a 64 K address of 00000H to 0FFFFH, because the vector code is assumed to be 2 bytes.

Of the 16-bit address, the lower 8 bits are stored at even addresses and the higher 8 bits are stored at odd addresses.

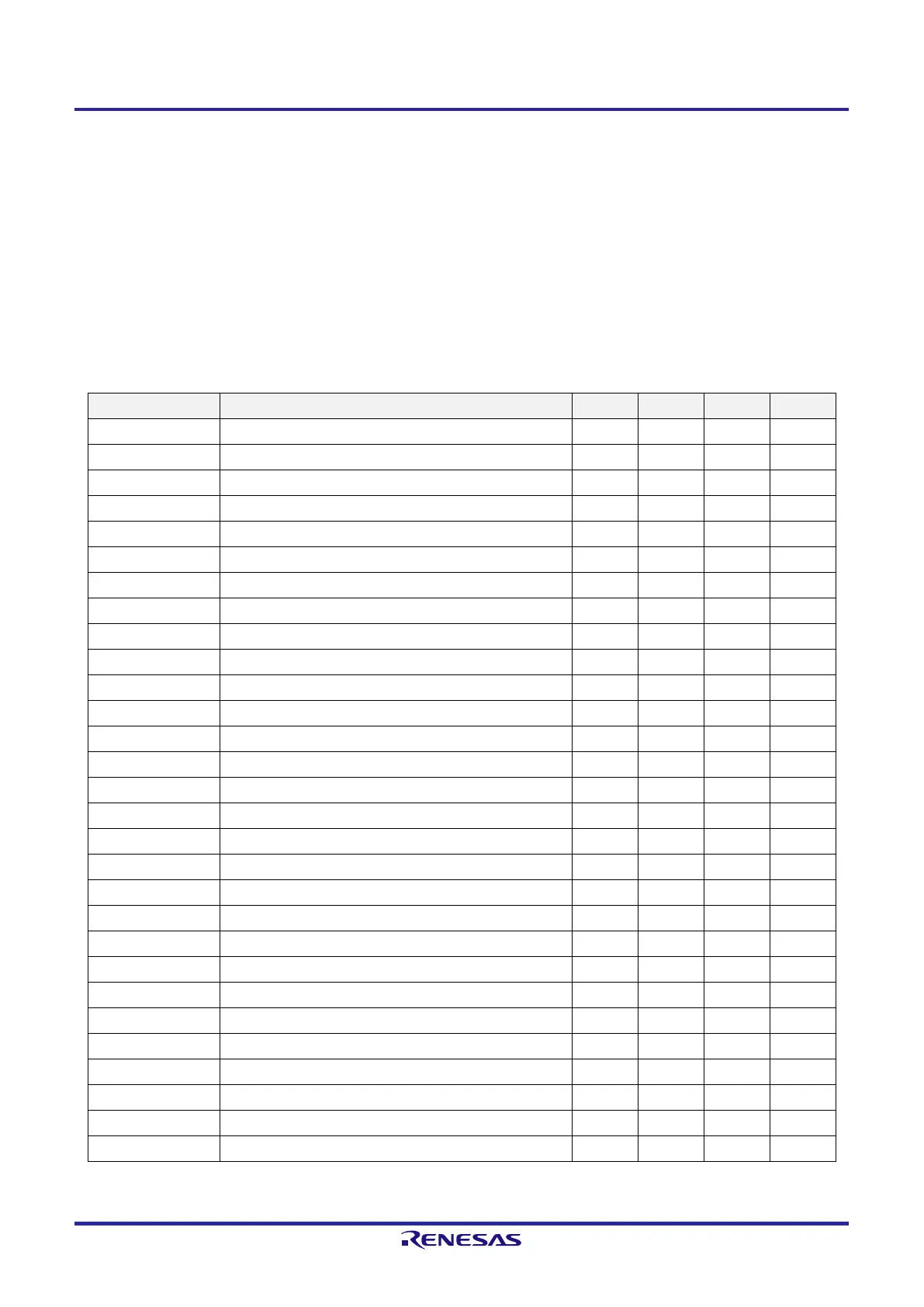

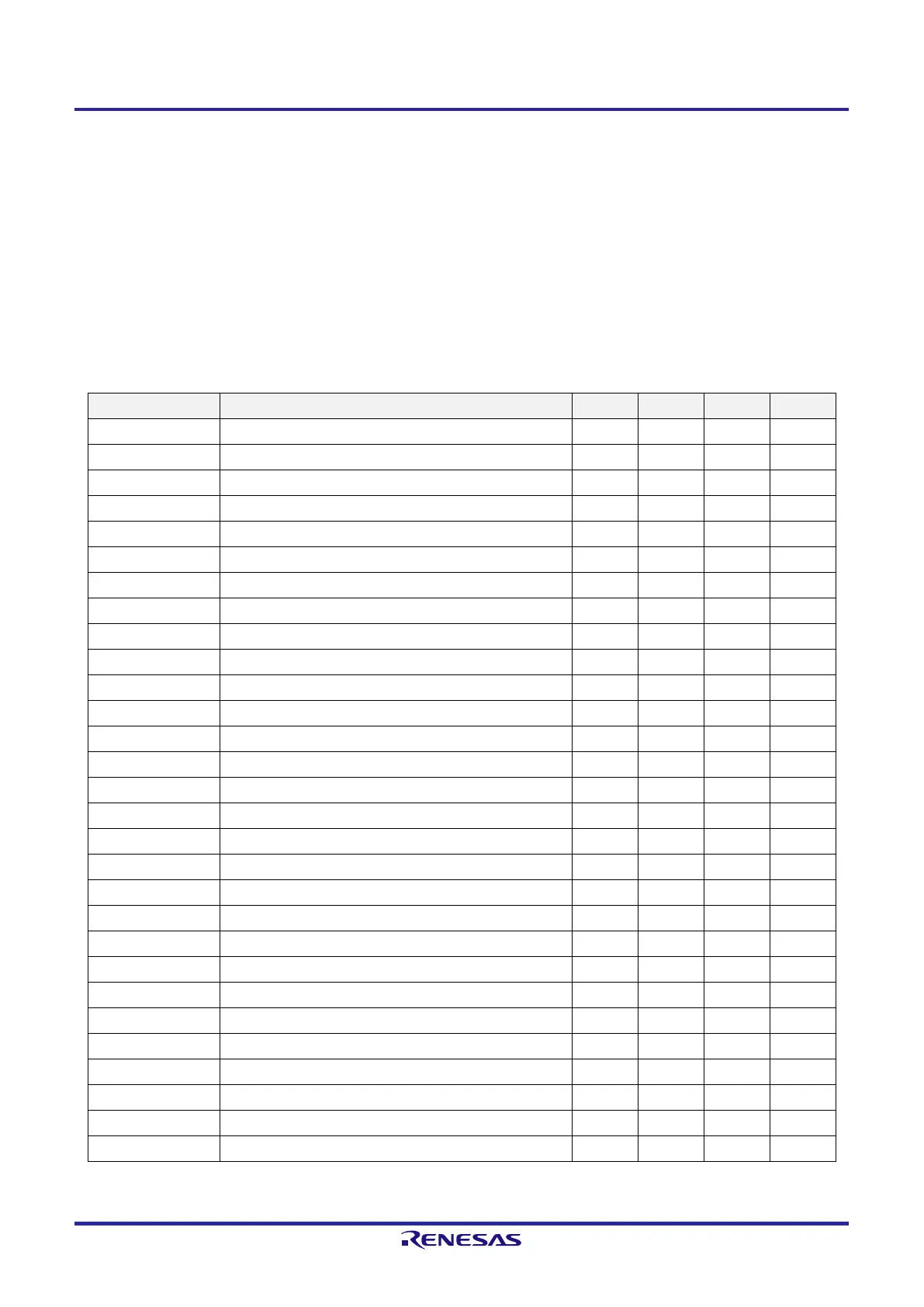

Table 3-3. Vector Table

Vector Table Address Interrupt Source 20-pin 16-pin 10-pin 8-pin

00000H RESET, SPOR, WDT, TRAP, IAW

00004H INTWDTI

00006H INTP0

00008H INTP1

0000AH INTP2

0000CH INTP3

0000EH INTP4

00010H INTP5

00012H INTST0, INTCSI00, INTIIC00

00014H INTSR0, INTCSI01, INTIIC01

00016H INTSRE0

00018H INTTM01H

0001AH INTTM00

0001CH INTTM01

0001EH INTAD

00020H INTP6 —

00022H INTP7 —

00024H INTTM03H

00026H INTIICA0

00028H INTTM02

0002AH INTTM03

0002CH INTIT

0002EH INTTM04

00030H INTTM05

00032H INTTM06

00034H INTTM07

00036H INTCMP0

00038H INTCMP1 — — —

0007EH BRK

Loading...

Loading...