Yes

FSSET register

No

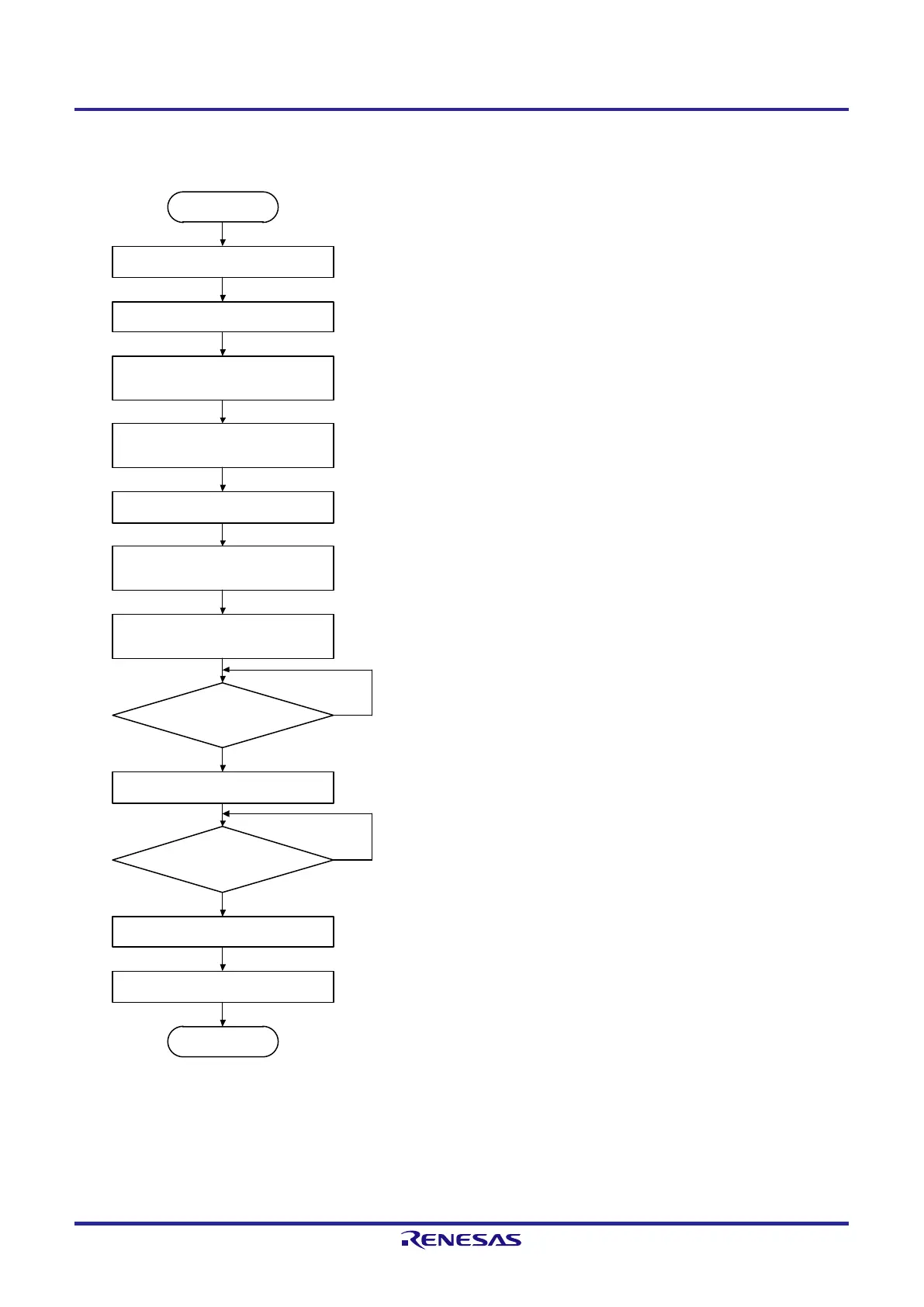

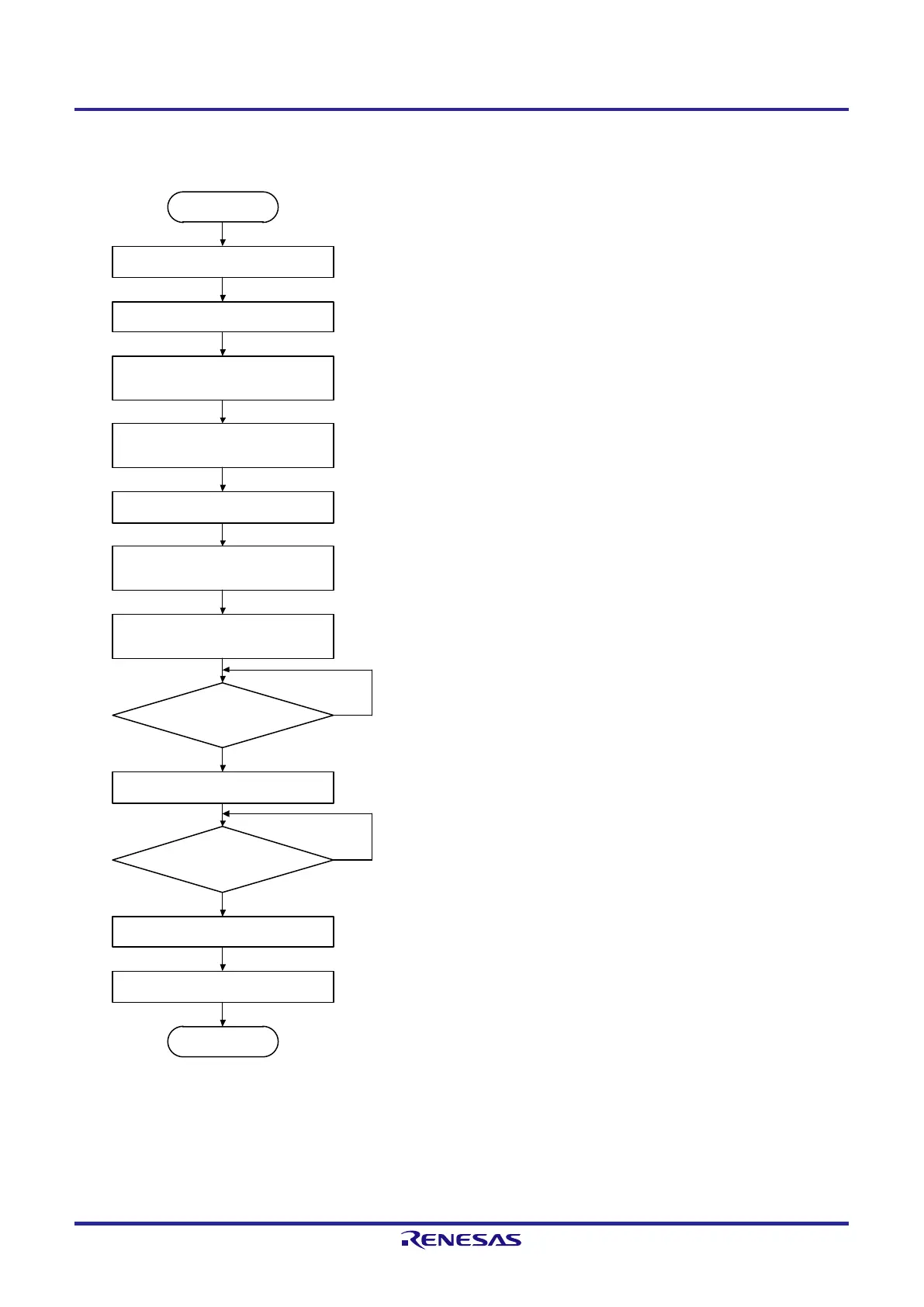

Start

End

Set the self-programming mode or area

Initial setting for the operating frequency

Check the sequencer operation

end status flag

Specify the address where rewriting

is to start

Specify the address where rewriting

is to end

Specify data to be written for rewriting

Specify the sequencer command for self-

programming to start the sequencer

The flash memory sequencer is activated

and the CPU enters the wait state

.

Check the error flag

End the self-programming mode

End the sequencer for self-programming

Check the sequencer operation

end status flag

No

Yes

FLPMC register

FLAPHG and FLAPL registers

FLSEDH and FLSEDL registers

FLWHH, FLWHL, FLWLH, and

FLWLL registers

FSSQ register

FSASTH register

FSSQ register

FSASTH register

FSASTL register

FLPMC register

Set the frequency of the CPU/peripheral hardware clock (f

CLK

) in

the FSET4-0 bits of the FSSET register.

Set the FWEDIS bit of the FLPMC register to 0 and set the

FLSPM bit to 1 at the same time.

To rewrite the data flash, set the SELDFL bit to 1 at the same

time.

Specify the start address for writing and block erasure.

Specify the end address of the block for block erasure.

For rewriting, set data to be written.

For block erasure, you do not have to set data.

Use the SQMD2-0 bits of the FSSQ register to select the

command for writing or block erasure and set the SQST bit to 1

to start the flash memory sequencer.

The flash memory sequencer is activated.

A CPU wait occurs.

The hardware waits until the CPU wait is released.

The SQEND bit in the FSASTH register is automatically set at the

end of the sequencer.

Check the SQEND bit in the FSASTH register and wait for the

completion of operation of the sequencer.

Confirm that the SQEND bit in the FSASTH register has been

automatically set and set the FSSQ register to

00

h.

The SEQER bit in the FSASTL being 0 and the given error bit

being 0 indicates normal completion.

If an error has occurred, you need to redo the steps over again.

Set the FLSPM bit of the FLPMC register to 0 to end the self-

programming mode.

Wait until the SQEND bit in the FSASTH register is cleared.

Loading...

Loading...