RL78/G15 CHAPTER 3 CPU ARCHITECTURE

R01UH0959EJ0110 Rev.1.10 Page 72 of 765

Mar 7, 2023

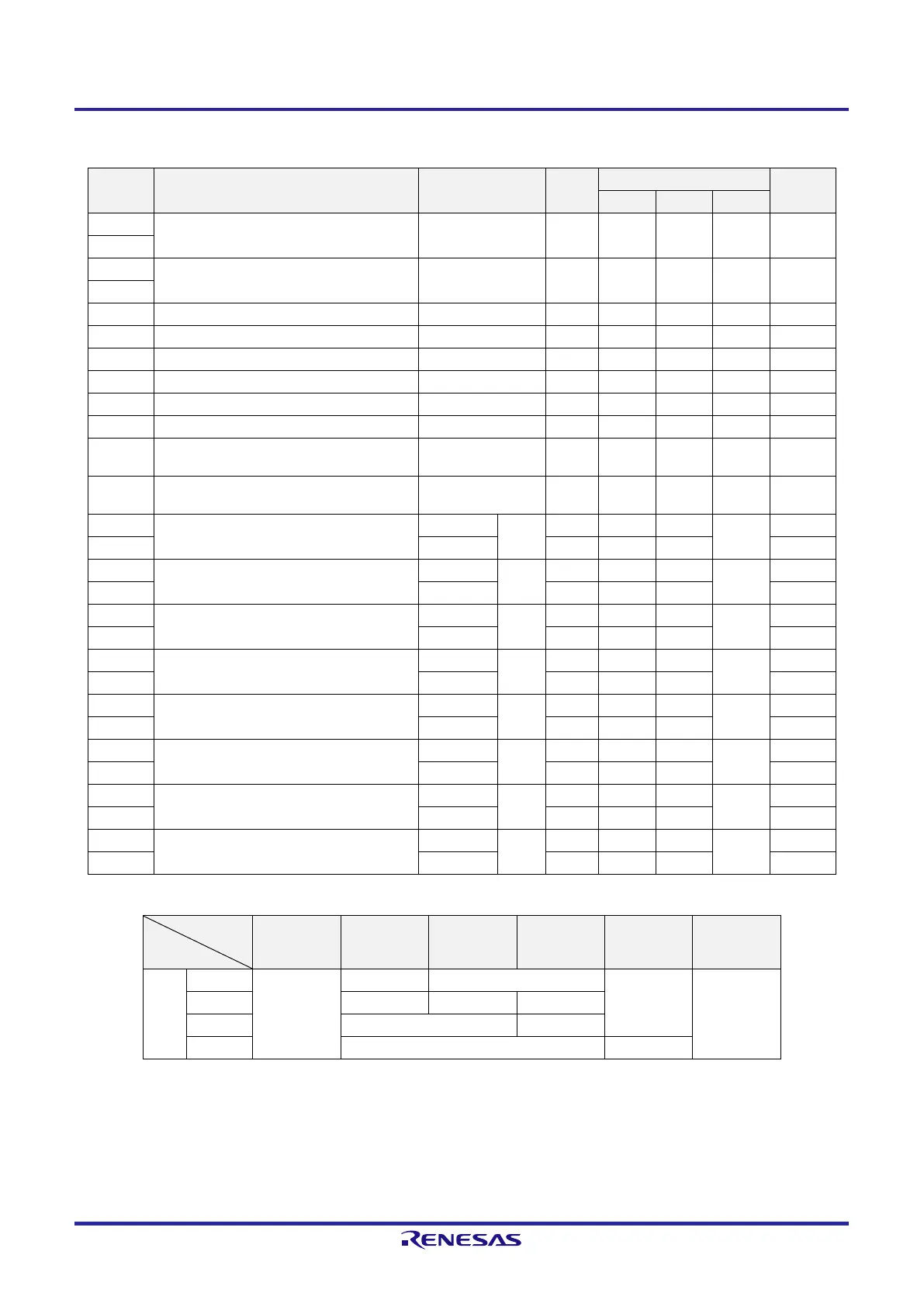

Table 3-5. SFR List (2/2)

Address Special Function Register (SFR) Name Symbol R/W Manipulable Bit Range After Reset

1-bit 8-bit 16-bit

FFF6EH Timer data register 07 TDR07 R/W — — 0000H

FFF6FH

FFF90H Interval timer control register ITMC R/W — — 0FFFH

FFF91H

FFFA0H Clock operation mode control register CMC R/W — — 00H

FFFA1H Clock operation status control register CSC R/W — 80H

FFFA2H Oscillation stabilization time counter status register OSTC R — 00H

FFFA3H Oscillation stabilization time select register OSTS R/W — — 07H

FFFA4H System clock control register CKC R/W — 00H

FFFA5H Clock output select register 0 CKS0 R/W — 00H

FFFA8H Reset control flag register RESF R — — Undefined

Note 1

FFFABH Watchdog timer enable register WDTE R/W — — 1AH/9AH

Note 2

FFFE0H Interrupt request flag register 0 IF0L IF0 R/W 00H

FFFE1H IF0H R/W 00H

FFFE2H Interrupt request flag register 1 IF1L IF1 R/W 00H

FFFE3H IF1H R/W 00H

FFFE4H Interrupt mask flag register 0 MK0L MK0 R/W FFH

FFFE5H MK0H R/W FFH

FFFE6H Interrupt mask flag register 1 MK1L MK1 R/W FFH

FFFE7H MK1H R/W FFH

FFFE8H Priority specification flag register 00 PR00L PR00 R/W FFH

FFFE9H PR00H R/W FFH

FFFEAH Priority specification flag register 01 PR01L PR01 R/W FFH

FFFEBH PR01H R/W FFH

FFFECH Priority specification flag register 10 PR10L PR10 R/W FFH

FFFEDH PR10H R/W FFH

FFFEEH Priority specification flag register 11 PR11L PR11 R/W FFH

FFFEFH PR11H R/W FFH

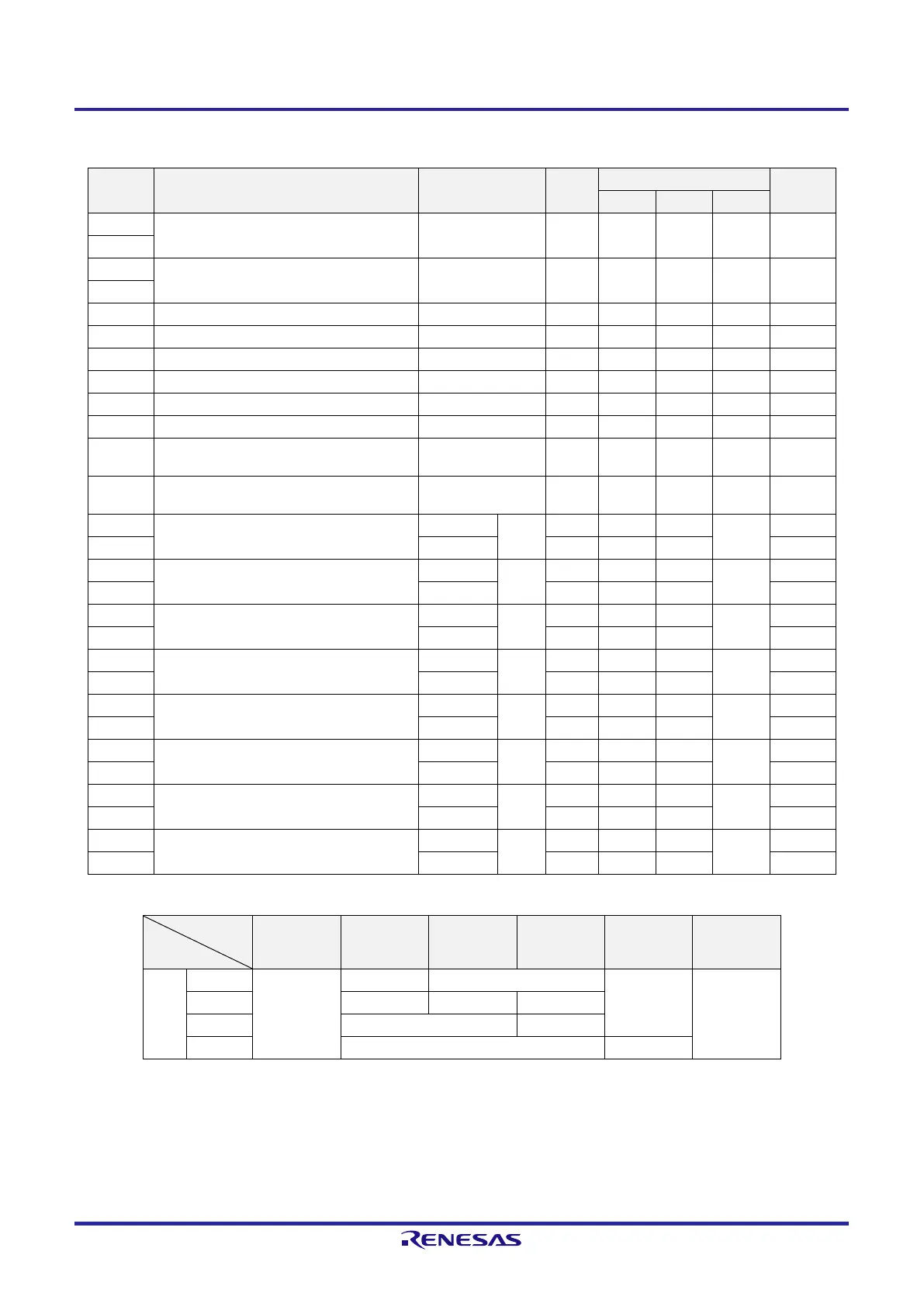

Note 1. The reset values of the registers vary depending on the reset source as shown below.

Reset Source

Register

RESET

Input Reset by

Execution of

Illegal Instruction

Reset by

WDT

Reset by

Illegal-Memory

Access

Reset by

SPOR

Reset by data

retention lower

limit voltage

RESF TRAP Cleared (0) Set (1) Held Held Cleared (0)

WDTRF Held Set (1) Held

IAWRF Held Set (1)

SPORF Held Set (1)

Note 2. The reset value of the WDTE register is determined by the setting of the option byte.

Remark For extended SFRs (2nd SFRs), see Table 3-6. Extended SFR (2nd SFR) List (1/4).

Loading...

Loading...