RL78/G15 CHAPTER 3 CPU ARCHITECTURE

R01UH0959EJ0110 Rev.1.10 Page 77 of 765

Mar 7, 2023

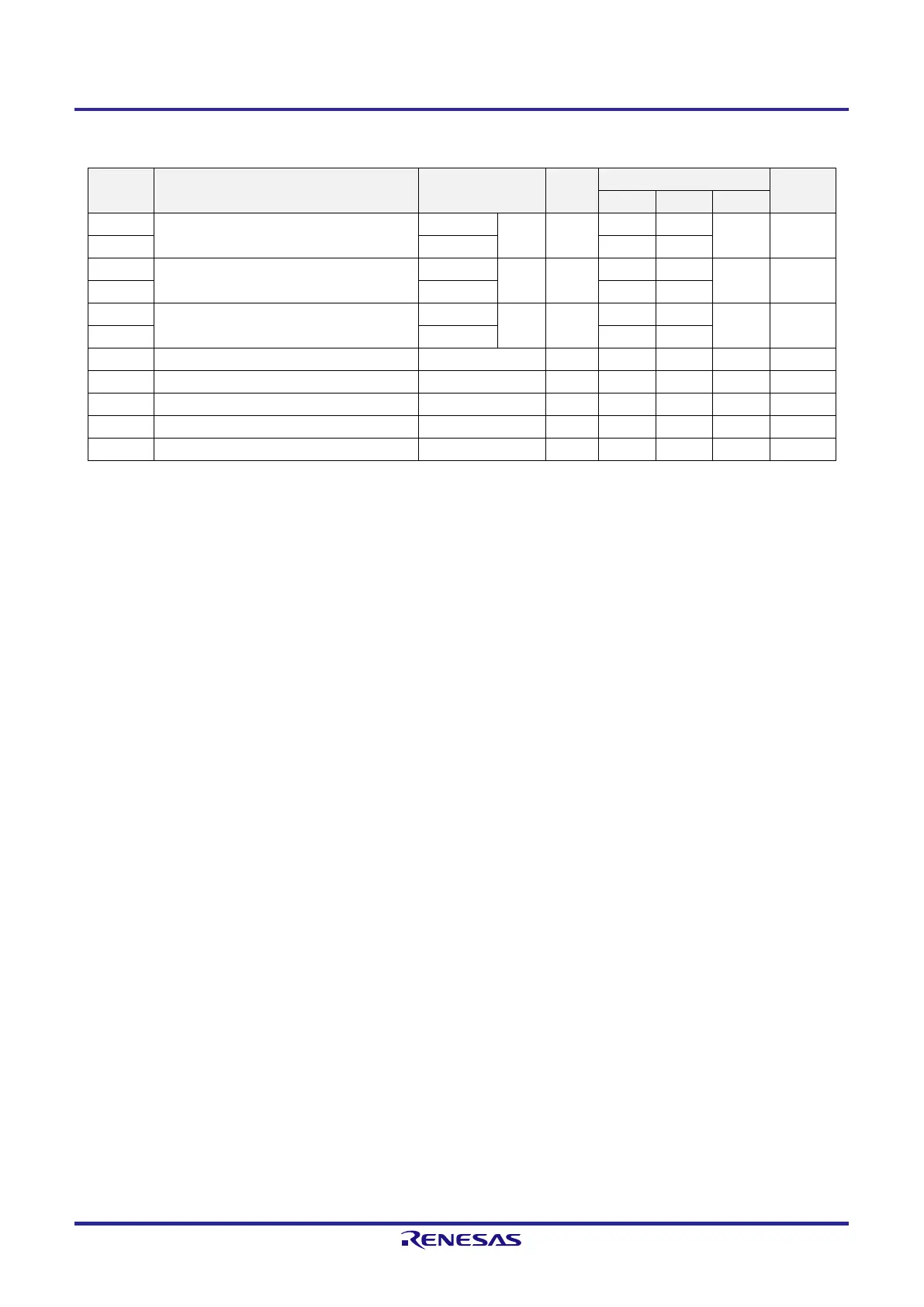

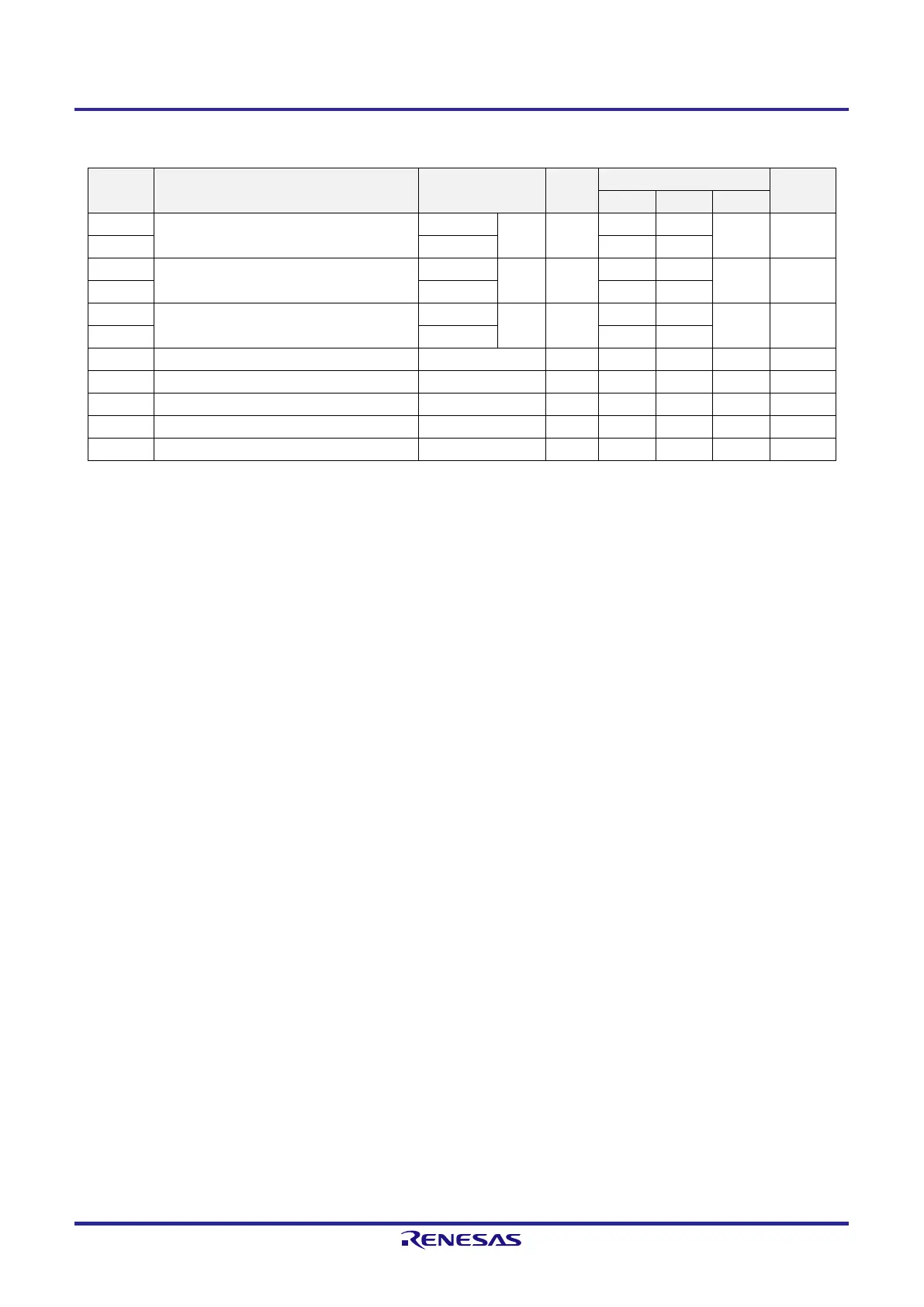

Table 3-6. Extended SFR (2nd SFR) List (4/4)

Address Special Function Register (SFR) Name Symbol R/W Manipulable Bit Range After Reset

1-bit 8-bit 16-bit

F01BAH Timer output enable register 0 TOE0L TOE0 R/W 0000H

F01BBH — — —

F01BCH Timer output level register 0 TOL0L TOL0 R/W — 0000H

F01BDH — — —

F01BEH Timer output mode register 0 TOM0L TOM0 R/W — 0000H

F01BFH — — —

F0230H IICA control register 00 IICCTL00 R/W — 00H

F0231H IICA control register 01 IICCTL01 R/W — 00H

F0232H IICA low-level width setting register 0 IICWL0 R/W — — FFH

F0233H IICA high-level width setting register 0 IICWH0 R/W — — FFH

F0234H Slave address register 0 SVA0 R/W — — 00H

Note 1. The value after a reset is adjusted at the time of shipment.

Note 2. The value is determined by the FRQSEL2 to FRQSEL0 settings in option byte 000C2H.

Remark For SFRs in the SFR area, see Table 3-5. SFR List (1/2).

Loading...

Loading...