Chapter 8: Configuration and Remote System Upgrades in Cyclone IV Devices 8–67

Configuration

May 2013 Altera Corporation Cyclone IV Device Handbook,

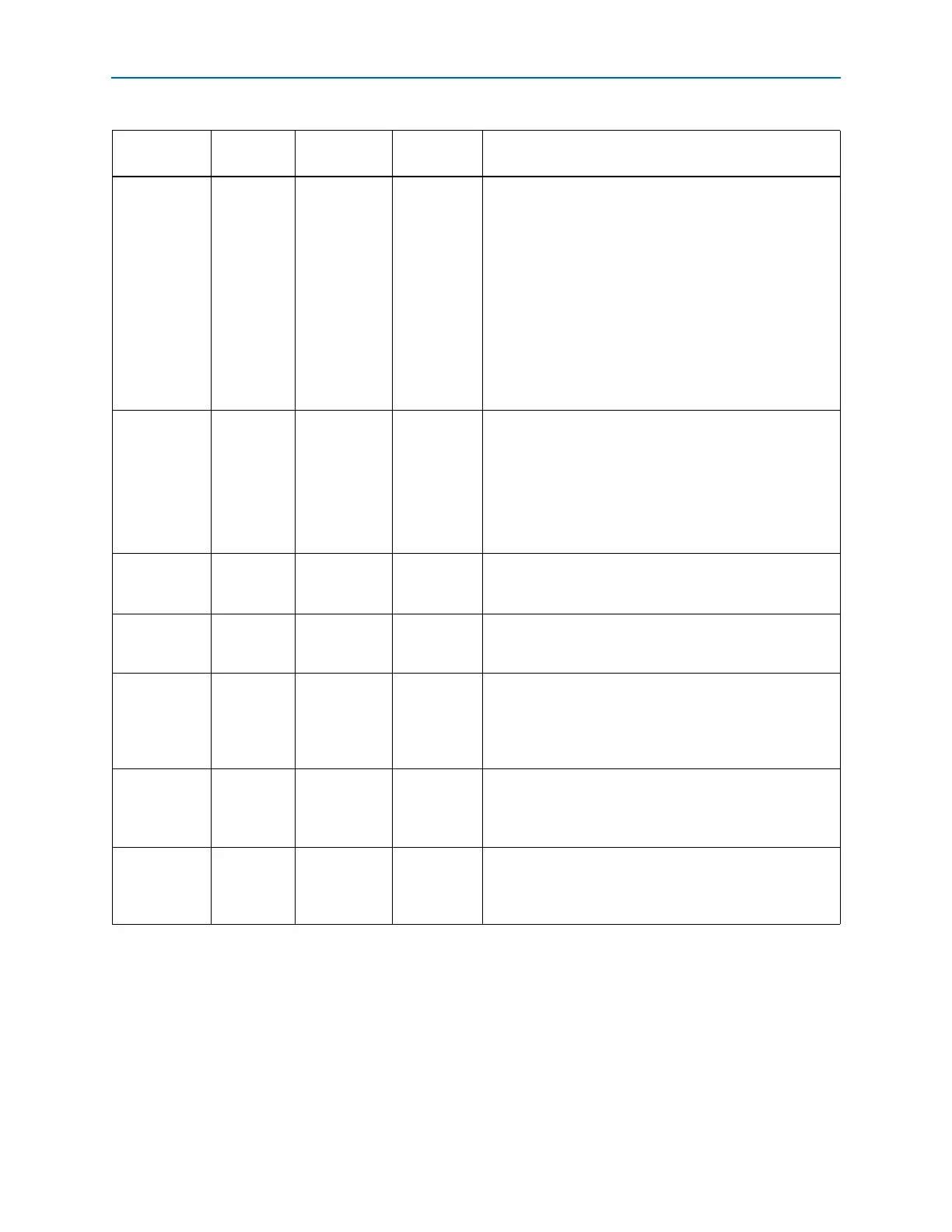

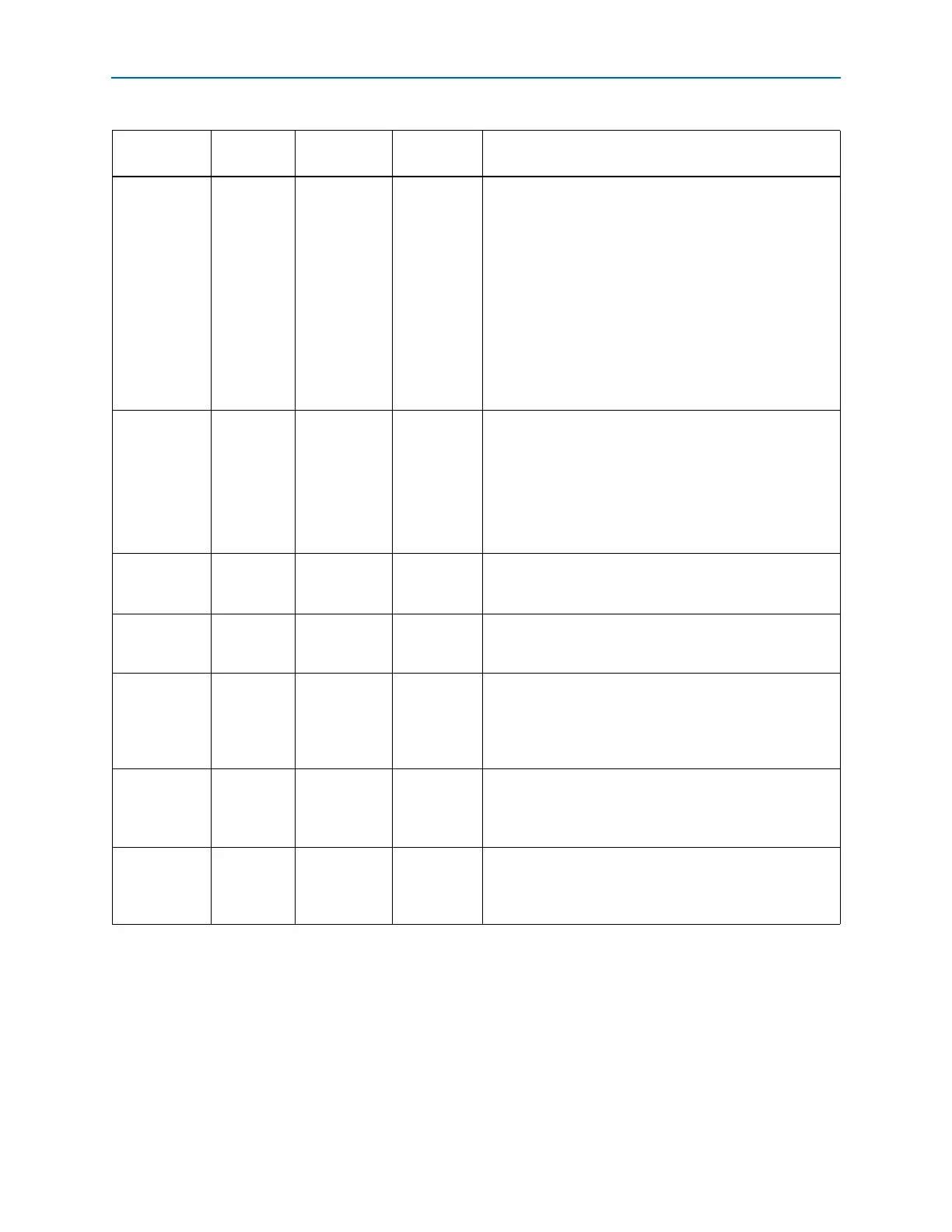

Volume 1

DATA[7..2]

I/O FPP, AP

(2)

Inputs (FPP).

Bidirectional

(AP)

(2)

In an AS or PS configuration scheme,

DATA[7..2]

function as user I/O pins during configuration, which

means they are tri-stated.

After FPP configuration,

DATA[7..2]

are available as user

I/O pins and the state of these pin depends on the

Dual-Purpose Pin settings.

In an AP configuration scheme, for Cyclone IV E devices

only, the byte-wide or word-wide configuration data is

presented to the target Cyclone IV E device on

DATA[7..0]

or

DATA[15..0]

, respectively. After AP configuration,

DATA[7..2]

are dedicated bidirectional pins with optional

user control.

(2)

DATA[15..8]

I/O AP

(2)

Bidirectional

Data inputs. Word-wide configuration data is presented to

the target Cyclone IV E device on

DATA[15..0]

.

In a PS, FPP, or AS configuration scheme,

DATA[15:8]

function as user I/O pins during configuration, which

means they are tri stated.

After AP configuration,

DATA[15:8]

are dedicated

bidirectional pins with optional user control.

PADD[23..0]

I/O AP

(2)

Output

In AP mode, it is a 24-bit address bus from the Cyclone IV E

device to the parallel flash. Connects to the

A[24:1]

bus on

the Micron P30 or P33 flash.

nRESET

I/O AP

(2)

Output

Active-low reset output. Driving the nRESET pin low resets

the parallel flash. Connects to the

RST#

pin on the Micron

P30 or P33 flash.

nAVD

I/O AP

(2)

Output

Active-low address valid output. Driving the nAVD pin low

during read or write operation indicates to the parallel flash

that a valid address is present on the

PADD[23..0]

address

bus. Connects to the

ADV#

pin on the Micron P30 or P33

flash.

nOE

I/O AP

(2)

Output

Active-low output enable to the parallel flash. During the

read operation, driving the

nOE

pin low enables the parallel

flash outputs (

DATA[15..0]

). Connects to the

OE#

pin on

the Micron P30 or P33 flash.

nWE

I/O AP

(2)

Output

Active-low write enable to the parallel flash. During the

write operation, driving the

nWE

pin low indicates to the

parallel flash that data on the

DATA[15..0]

bus is valid.

Connects to the

WE#

pin on the Micron P30 or P33 flash.

Note to Table 8–20:

(1) If you are accessing the EPCS device with the ALTASMI_PARALLEL megafunction or your own user logic in user mode, in the Device and Pin

Options window of the Quartus II software, in the Dual-Purpose Pins category, select Use as regular I/O for this pin.

(2) The AP configuration scheme is for Cyclone IV E devices only.

Table 8–20. Dedicated Configuration Pins on the Cyclone IV Device (Part 4 of 4)

Pin Name User Mode

Configuration

Scheme

Pin Type Description

Loading...

Loading...