9–8 Chapter 9: SEU Mitigation in Cyclone IV Devices

Software Support

Cyclone IV Device Handbook, May 2013 Altera Corporation

Volume 1

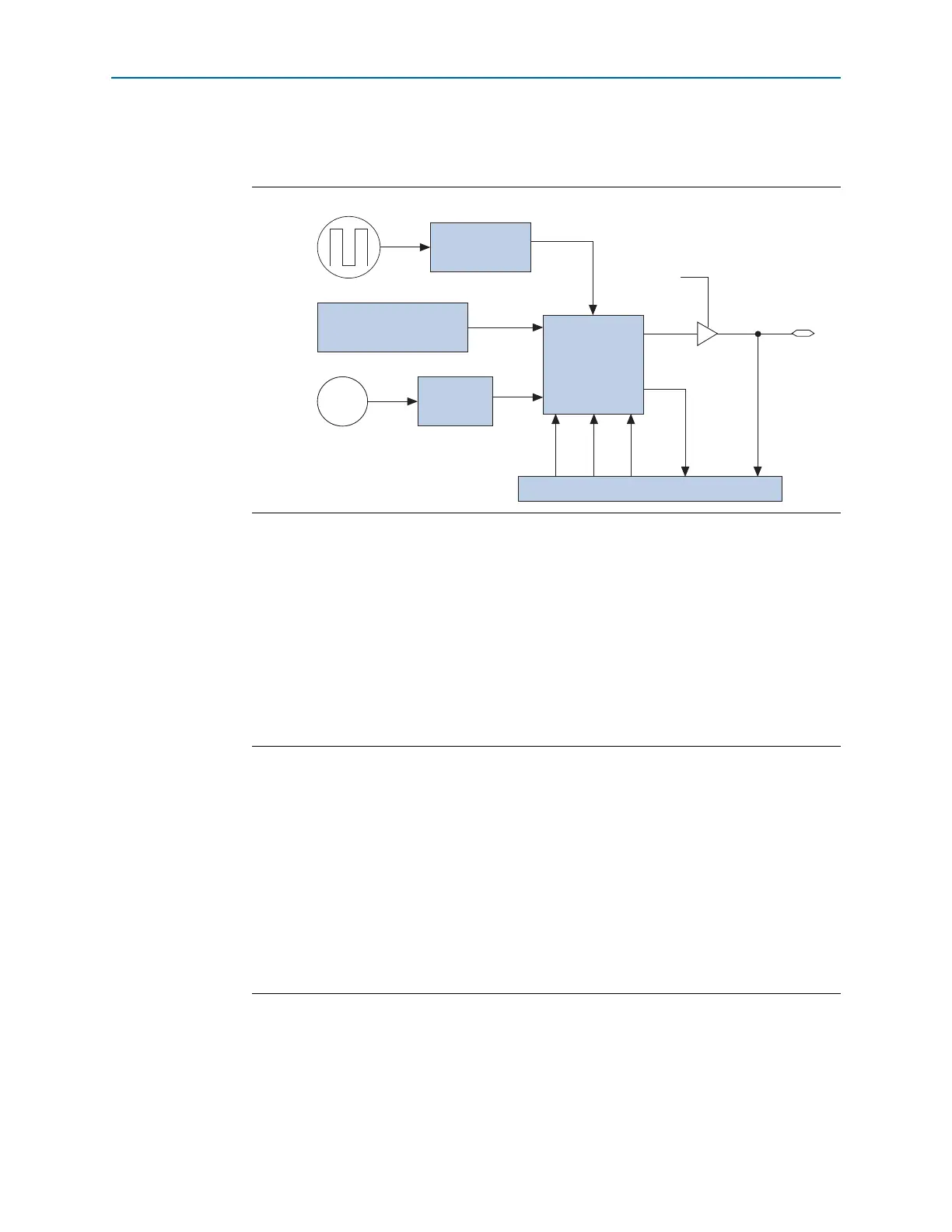

Figure 9–3 shows the error detection block diagram in FPGA devices and shows the

interface that the WYSIWYG atom enables in your design.

1 The user logic is affected by the soft error failure, so reading out the 32-bit CRC

signature through the

regout

should not be relied upon to detect a soft error. You

should rely on the

CRC_ERROR

output signal itself, because this

CRC_ERROR

output

signal cannot be affected by a soft error.

To enable the

cycloneiv_crcblock

WYSIWYG atom, you must name the atom for

each Cyclone IV device accordingly.

Example 9–1 shows an example of how to define the input and output ports of a

WYSIWYG atom in a Cyclone IV device.

Figure 9–3. Error Detection Block Diagram

Clock Divider

(1 to 256 Factor)

Pre-Computed CRC

(Saved in the Option Register)

CRC

Computation

Error Detection

Logic

SRAM

Bits

CRC_ERROR

(Shown in BIDIR Mode)

V

CC

Logic Array

CLK

SHIFTNLD

LDSRC

REGOUT

CRC_ERROR

80 MHz Internal Chip Oscillator

Example 9–1. Error Detection Block Diagram

cycloneiv_crcblock<crcblock_name>

(

.clk(<clock source>),

.shiftnld(<shiftnld source>),

.ldsrc(<ldsrc source>),

.crcerror(<crcerror out destination>),

.regout(<output destination>),

);

Loading...

Loading...