Chapter 1: Cyclone IV Transceivers Architecture 1–7

Transmitter Channel Datapath

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

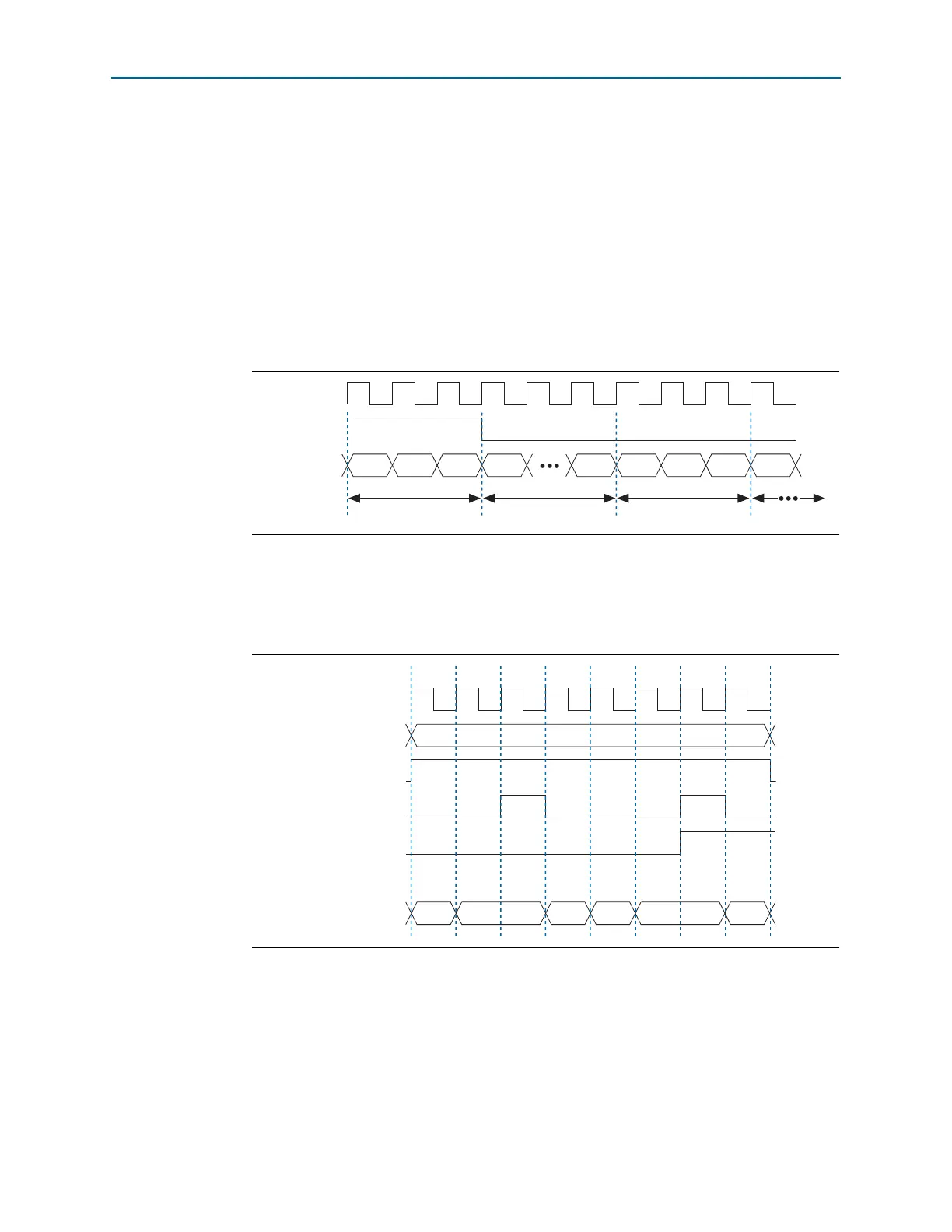

The following describes the 8B/10B encoder behavior in reset condition (as shown in

Figure 1–7):

■ During reset, the 8B/10B encoder ignores the inputs (

tx_datain

and

tx_ctrlenable

ports) from the FPGA fabric and outputs the K28.5 pattern from

the RD- column continuously until the

tx_digitalreset

port is deasserted.

■ Upon deassertion of the

tx_digitalreset

port, the 8B/10B encoder starts with a

negative disparity and transmits three K28.5 code groups for synchronization

before it starts encoding and transmitting data on its output.

■ Due to some pipelining of the transmitter PCS, some "don't cares" (10'hxxx) are

sent before the three synchronizing K28.5 code groups.

The encoder supports forcing the running disparity to either positive or negative

disparity with

tx_forcedisp

and

tx_dispval

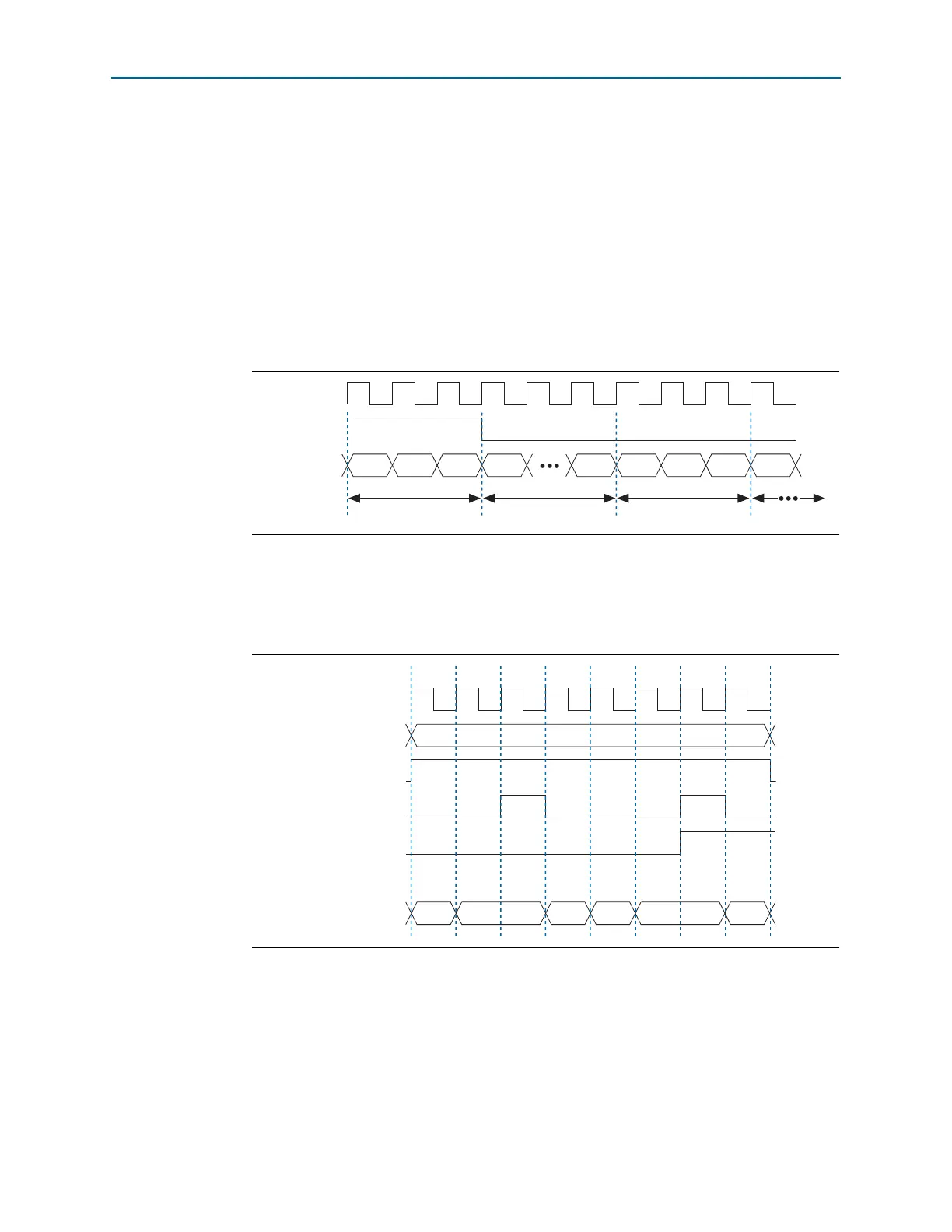

ports. Figure 1–8 shows an example of

tx_forcedisp

and

tx_dispval

port use, where data is shown in hexadecimal radix.

In this example, a series of K28.5 code groups are continuously sent. The stream

alternates between a positive disparity K28.5 (RD+) and a negative disparity K28.5

(RD-) to maintain a neutral overall disparity. The current running disparity at time

n + 1 indicates that the K28.5 in time n + 2 should be encoded with a negative

disparity. Because

tx_forcedisp

is high at time n + 2, and

tx_dispval

is low, the K28.5

Figure 1–7. 8B/10B Encoder Behavior in Reset Condition

Figure 1–8. Force Running Disparity Operation

tx_digitalreset

clock

During reset

dataout[9..0] K28.5- K28.5- K28.5- xxx xxx K28.5+K28.5- K28.5- Dx.y+

Don’t cares after reset Synchronization Normal

operation

tx_ctrlenable

clock

n n + 1 n + 2 n + 3 n + 4

tx_forcedisp

tx_disp

val

Current Disparity RD- RD+ RD+ RD- RD- RD+RD- RD+

dataout[9..0] 17C 283 17C 17C283 283

txin[7..0]

BC

n + 5 n + 6 n + 7

Loading...

Loading...