1–40 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Clocking Architecture

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

When the byte serializer is enabled, the common bonded low-speed clock frequency is

halved before feeding to the read clock of TX phase compensation FIFO. The common

bonded low-speed clock is available in FPGA fabric as

coreclkout

port, which can be

used in FPGA fabric to send transmitter data and control signals to the bonded

channels.

1 Bonded channel configuration is not available for Receiver Only channel operation

because each of the channels are individually clocked by its recovered clock.

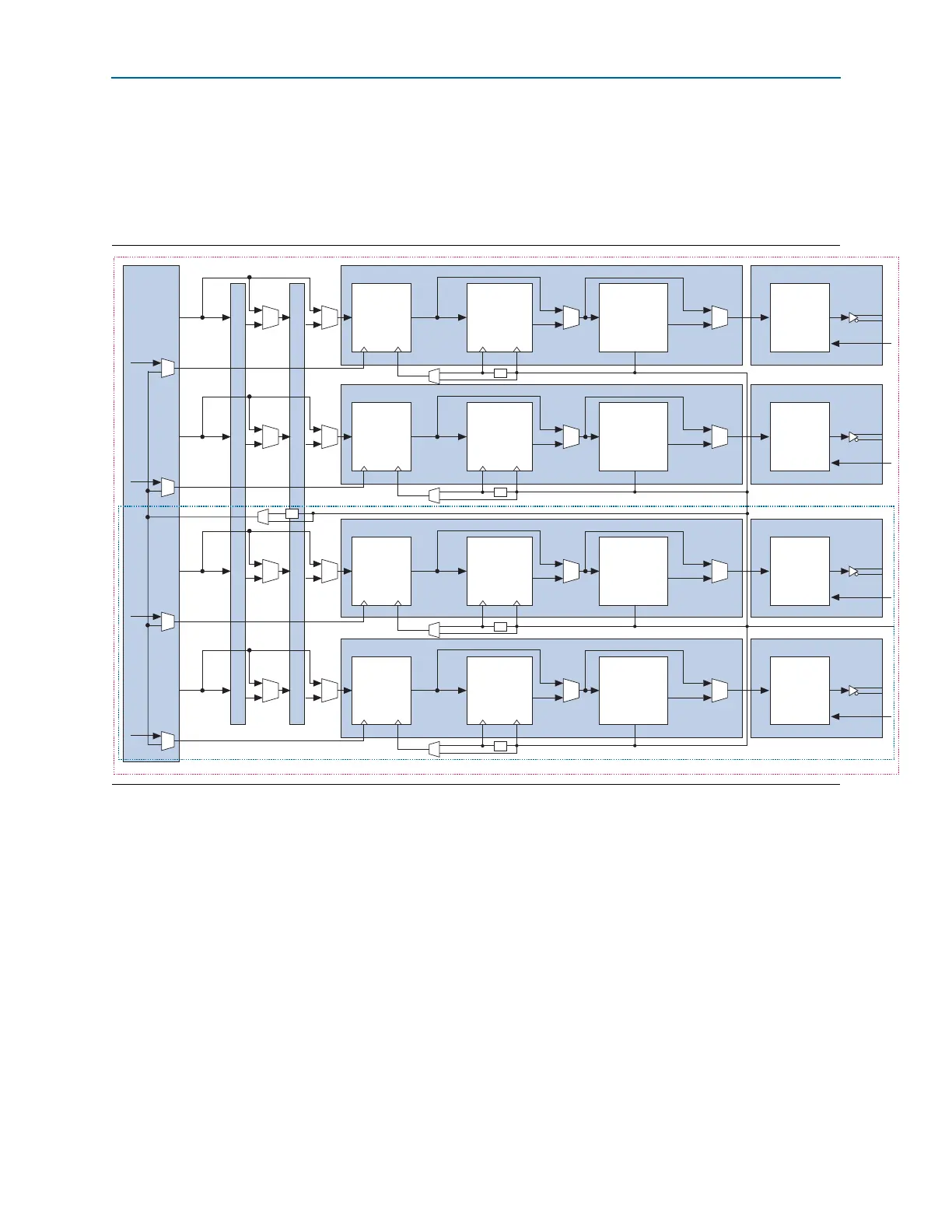

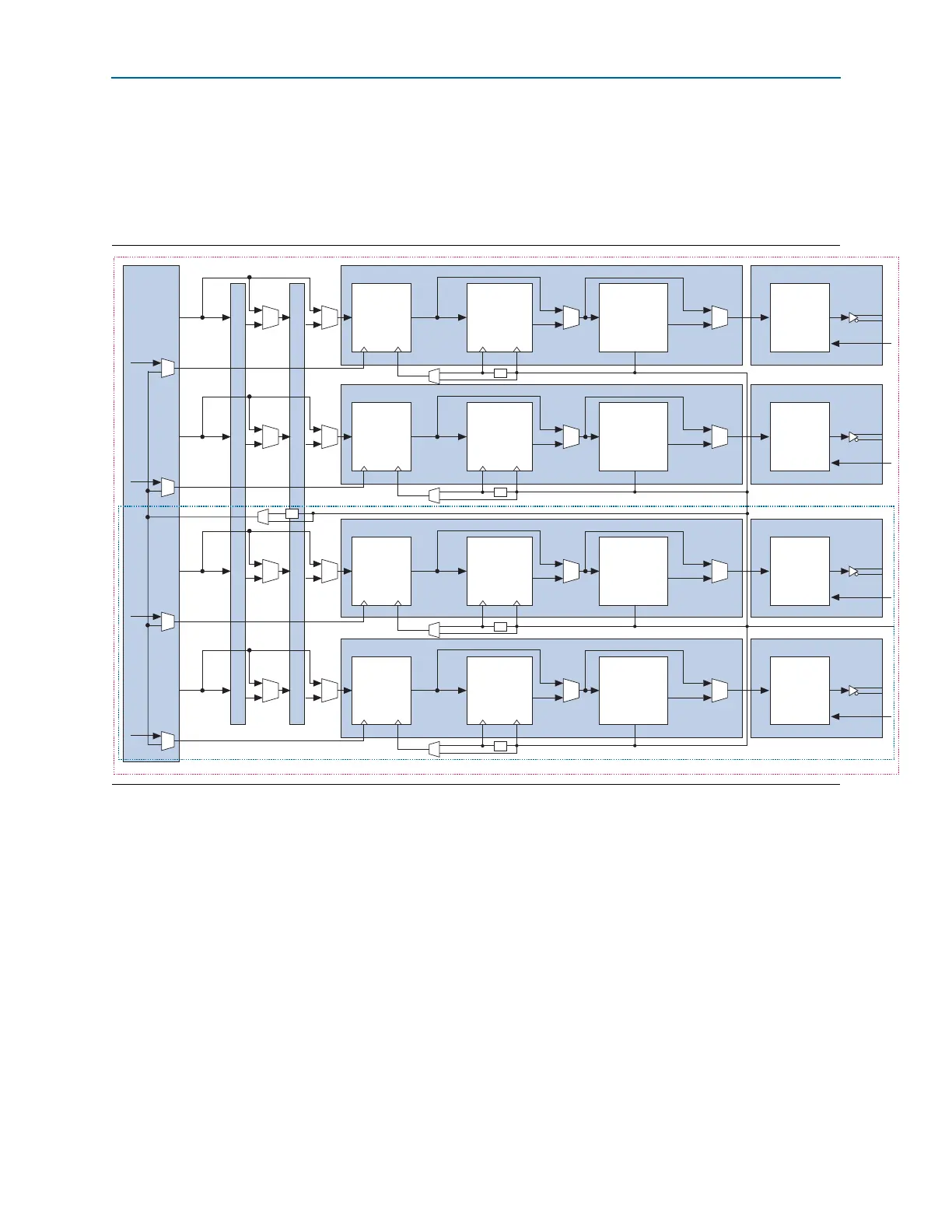

Figure 1–38. Transmitter Only Datapath Clocking in Bonded Channel Configuration

Byte Serializer

8B/10B Encoder

Transmitter Channel PCS 3 Transmitter Channel PMA 3

Serializer

PCIe Hard IP

FPGA

Fabric

PIPE Interface

Tx Phase

Comp

FIFO

wr_clk rd_clk

wr_clk rd_clk

high-speed

clock

tx_dataout[3]

coreclkout

In 2 Bonded Channel Configuration

+

tx_coreclk[3]

Byte Serializer

8B/10B Encoder

Transmitter Channel PCS 2 Transmitter Channel PMA 2

Serializer

Tx Phase

Comp

FIFO

wr_clk rd_clk

wr_clk rd_clk

high-speed

clock

/2

/2

tx_dataout[2]

tx_coreclk[2]

Byte Serializer

8B/10B Encoder

Transmitter Channel PCS 1 Transmitter Channel PMA 1

Serializer

Tx Phase

Comp

FIFO

wr_clk rd_clk

wr_clk rd_clk

high-speed

clock

/2

tx_dataout[1]

tx_coreclk[1]

Byte Serializer

8B/10B Encoder

Transmitter Channel PCS 0 Transmitter Channel PMA 0

Serializer

Tx Phase

Comp

FIFO

wr_clk rd_clk

wr_clk rd_clk

high-speed

clock

/2

tx_dataout[0]

tx_coreclk[0]

In 4 Bonded Channel Configuration

+

/2

low-speed clock

Loading...

Loading...