Chapter 1: Cyclone IV Transceivers Architecture 1–39

Transceiver Clocking Architecture

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

The channel datapath clocking is similar between bonded channels in ×2 and ×4

configurations.

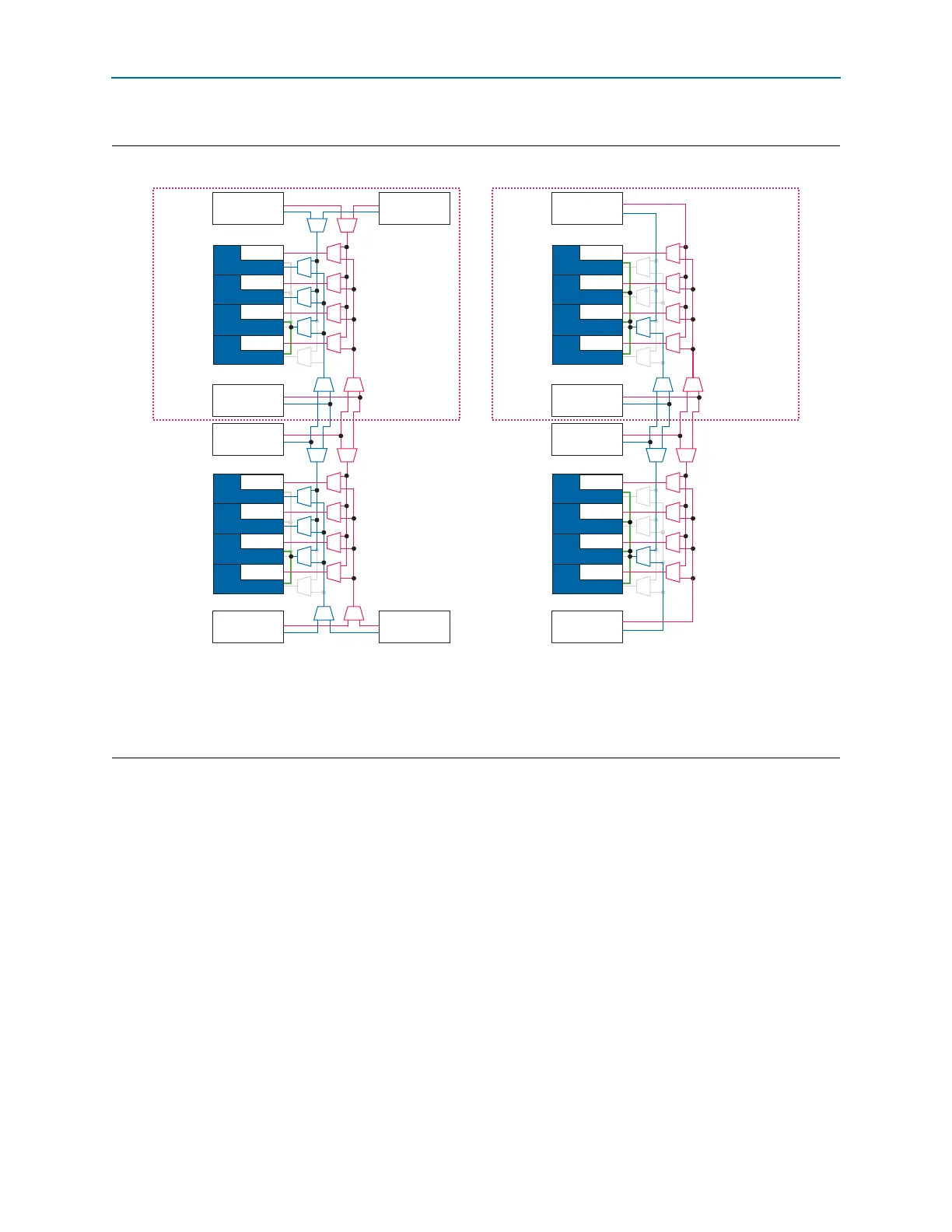

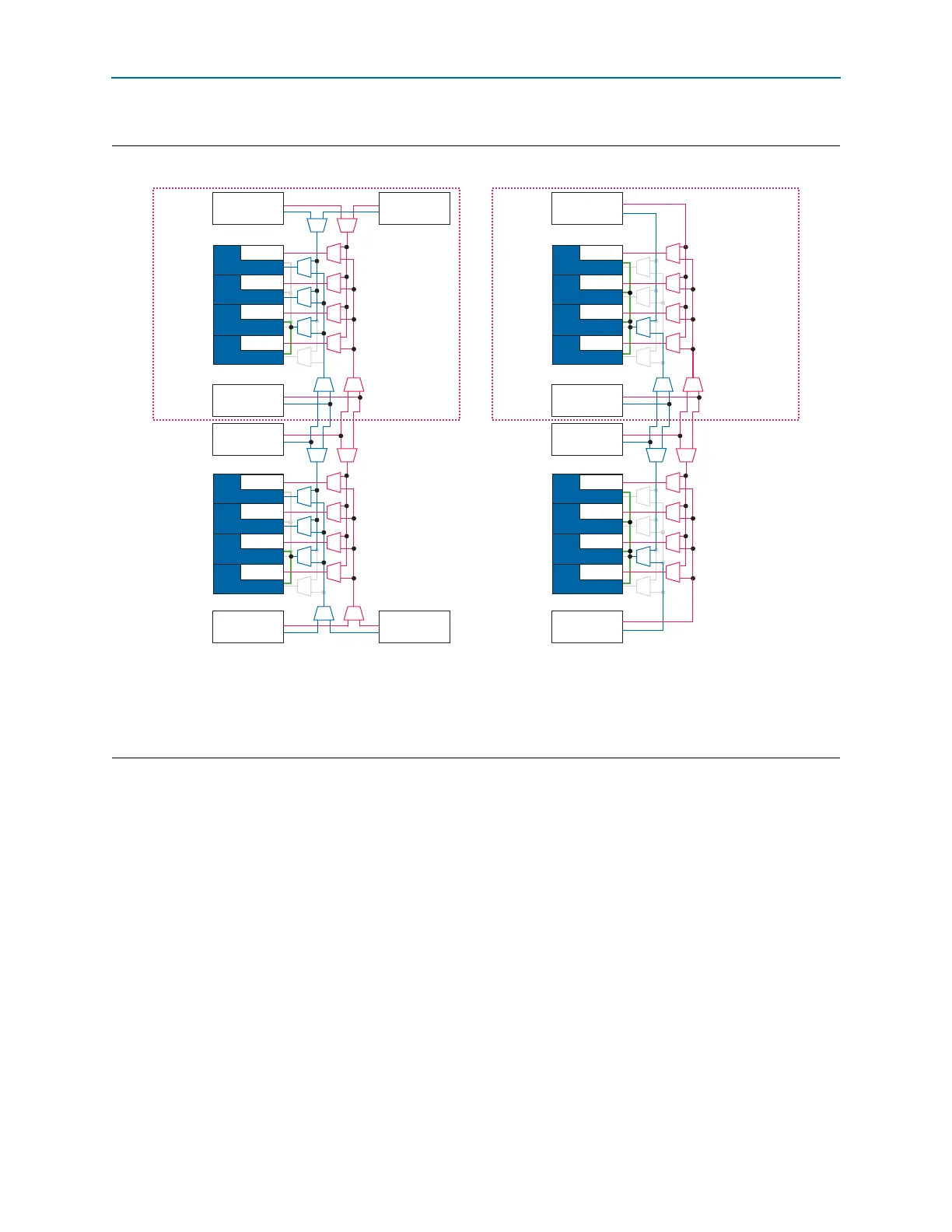

Figure 1–38 shows the datapath clocking in Transmitter Only operation for ×2 and ×4

bonded configurations. In these configurations, each bonded channel selects the

high-speed clock from one the supported PLLs. The high-speed clock in each bonded

channel feeds the respective serializer for parallel to serial operation. The common

bonded low-speed clock feeds to each bonded channel that is used for the following

blocks in each transmitter PCS channel:

■ 8B/10B encoder

■ read clock of byte serializer

■ read clock of TX phase compensation FIFO

Figure 1–37. Clock Distribution in Bonded (×2 and ×4) Channel Configuration for Transceivers in F484 and Larger

Packages

Notes to Figure 1–37:

(1) High-speed clock.

(2) Low-speed clock.

(3) Bonded common low-speed clock path.

(4) These PLLs have restricted clock driving capability and may not reach all connected channels. For details, refer to Table 1–10.

(3)

Not applicable in

F484 package

Transceiver

Block

GXBL1

MPLL_8

MPLL_7

(1)

(2)

(1)

(2)

Transceiver

Block

GXBL0

MPLL_6

MPLL_5

GPLL_2

GPLL_1

(4)

(4)

2 Bonded Channel Configuration

+

4 Bonded Channel Configuration

+

TX PMA

TX PMA

TX PMA

TX PMA

Ch3

Ch2

Ch3

Ch2

Ch1

Ch0

TX PMA

TX PMA

TX PMA

TX PMA

Ch1

Ch0

(3)

(3)

Not applicable in

F484 package

Transceiver

Block

GXBL1

MPLL_8

MPLL_7

(1)

(2)

(1)

(2)

Transceiver

Block

GXBL0

MPLL_6

MPLL_5

TX PMA

TX PMA

TX PMA

TX PMA

Ch3

Ch2

Ch3

Ch2

Ch1

Ch0

TX PMA

TX PMA

TX PMA

TX PMA

Ch1

Ch0

(3)

Loading...

Loading...