3–8 Chapter 3: Cyclone IV Dynamic Reconfiguration

Dynamic Reconfiguration Controller Port List

Cyclone IV Device Handbook, November 2011 Altera Corporation

Volume 2

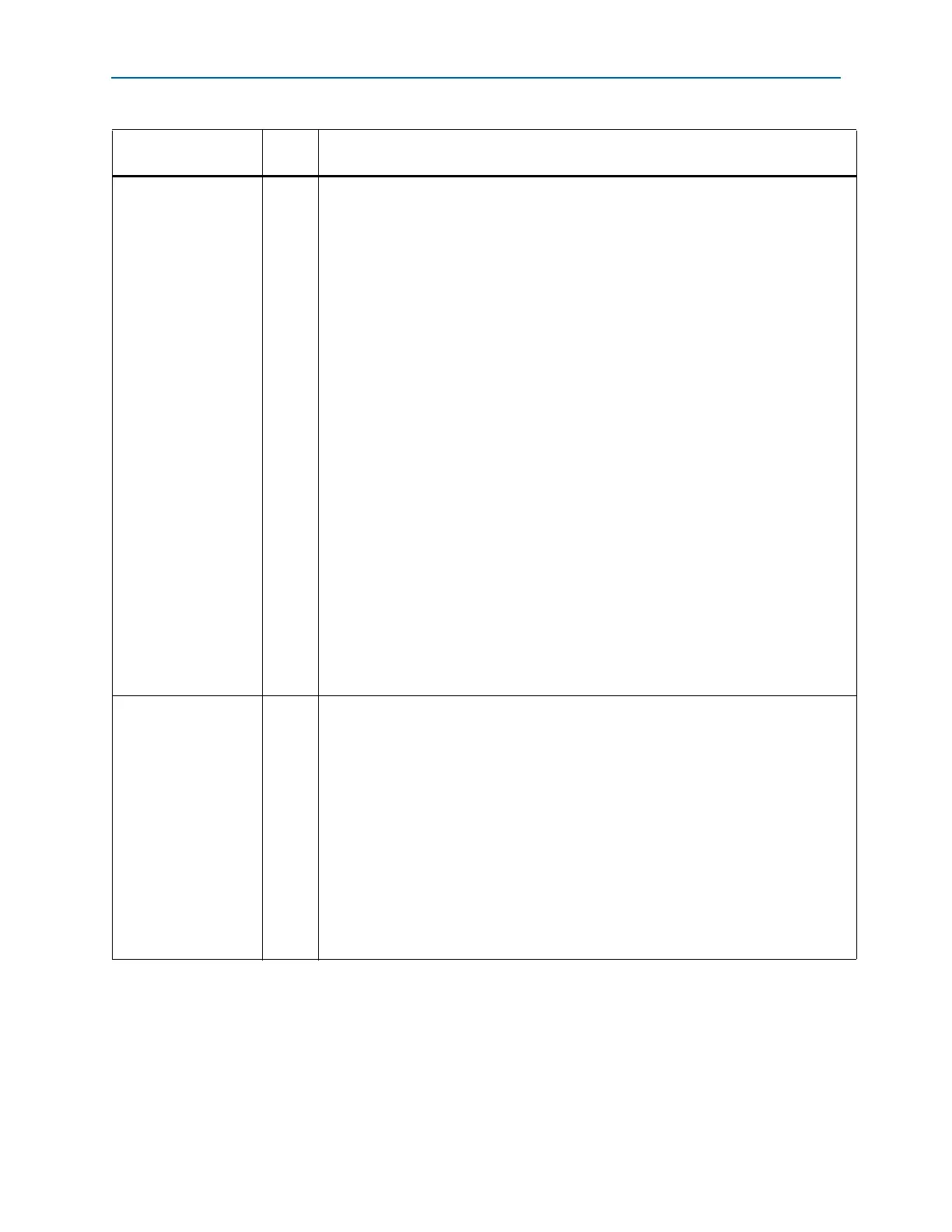

tx_preemp[4..0]

(1)

Input

This is an optional pre-emphasis write control for the transmit buffer. Depending on what

value you set at this input, the controller dynamically writes the value to the pre-emphasis

control register of the transmit buffer.

The width of this signal is fixed to 5 bits if you enable either the Use

'logical_channel_address' port for Analog controls reconfiguration option or the Use

same control signal for all the channels option in the Analog controls screen. Otherwise,

the width of this signal is 5 bits per channel.

tx_preemp[4..0]

Corresponding ALTGX Corresponding pre-

instance settings emphasis setting (mA)

00000 0 Disabled

00001 1 0.5

00101 5 1.0

01001 9 1.5

01101 13 2.0

10000 16 2.375

10001 17 2.5

10010 18 2.625

10011 19 2.75

10100 20 2.875

10101 21 3.0

All other values => N/A

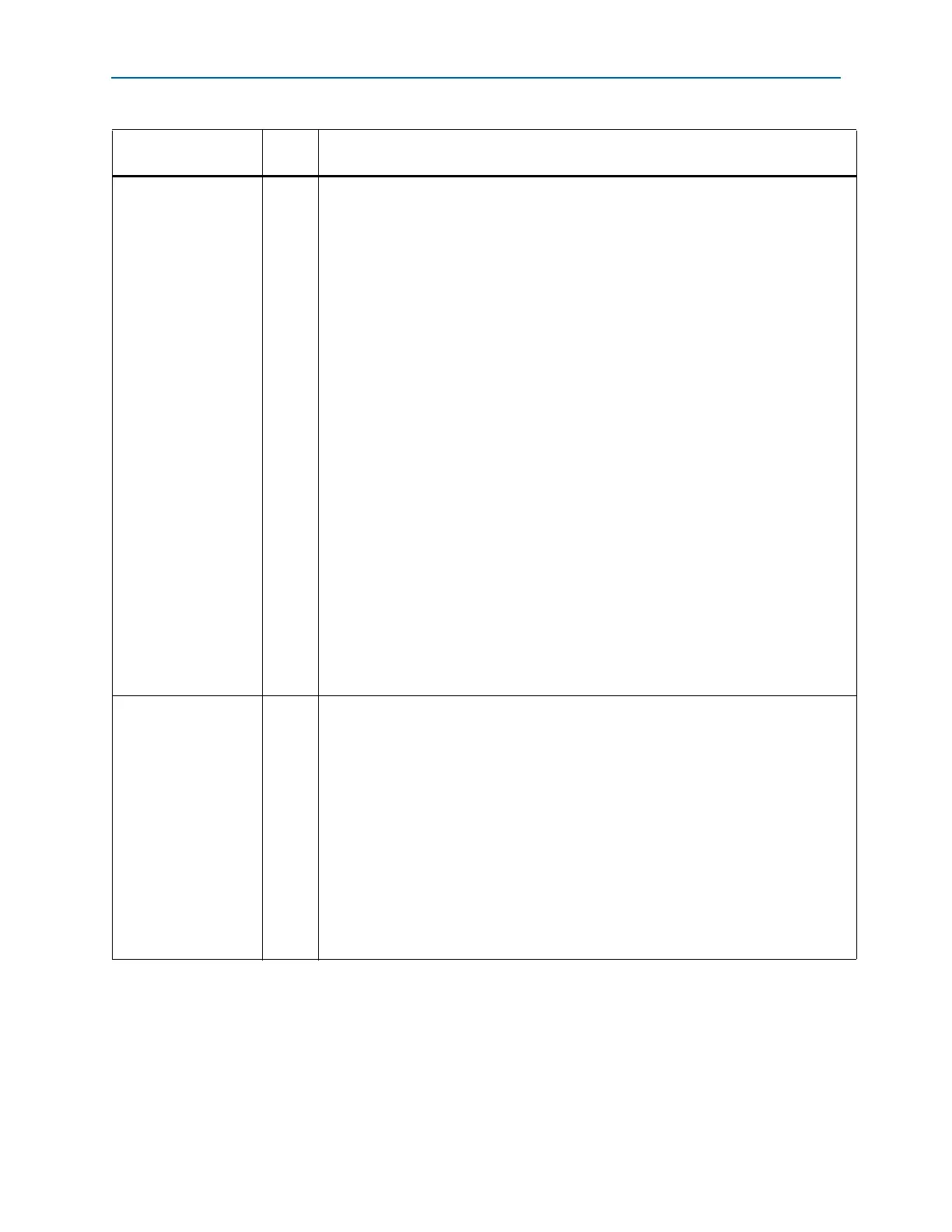

rx_eqctrl[3..0]

(1)

Input

This is an optional write control to write an equalization control value for the receive side of

the PMA.

The width of this signal is fixed to 4 bits if you enable either the Use

'logical_channel_address' port for Analog controls reconfiguration option or the Use

same control signal for all the channels option in the Analog controls screen. Otherwise,

the width of this signal is 4 bits per channel.

rx_eqctrl[3..0]

Corresponding ALTGX instance settings

0001 Low

0101 Medium Low

0100 Medium High

0111 High

All other values => N/A

Table 3–2. Dynamic Reconfiguration Controller Port List (ALTGX_RECONFIG Instance) (Part 5 of 7)

Port Name

Input/

Output

Description

Loading...

Loading...