Chapter 3: Cyclone IV Dynamic Reconfiguration 3–31

Dynamic Reconfiguration Modes

November 2011 Altera Corporation Cyclone IV Device Handbook,

Volume 2

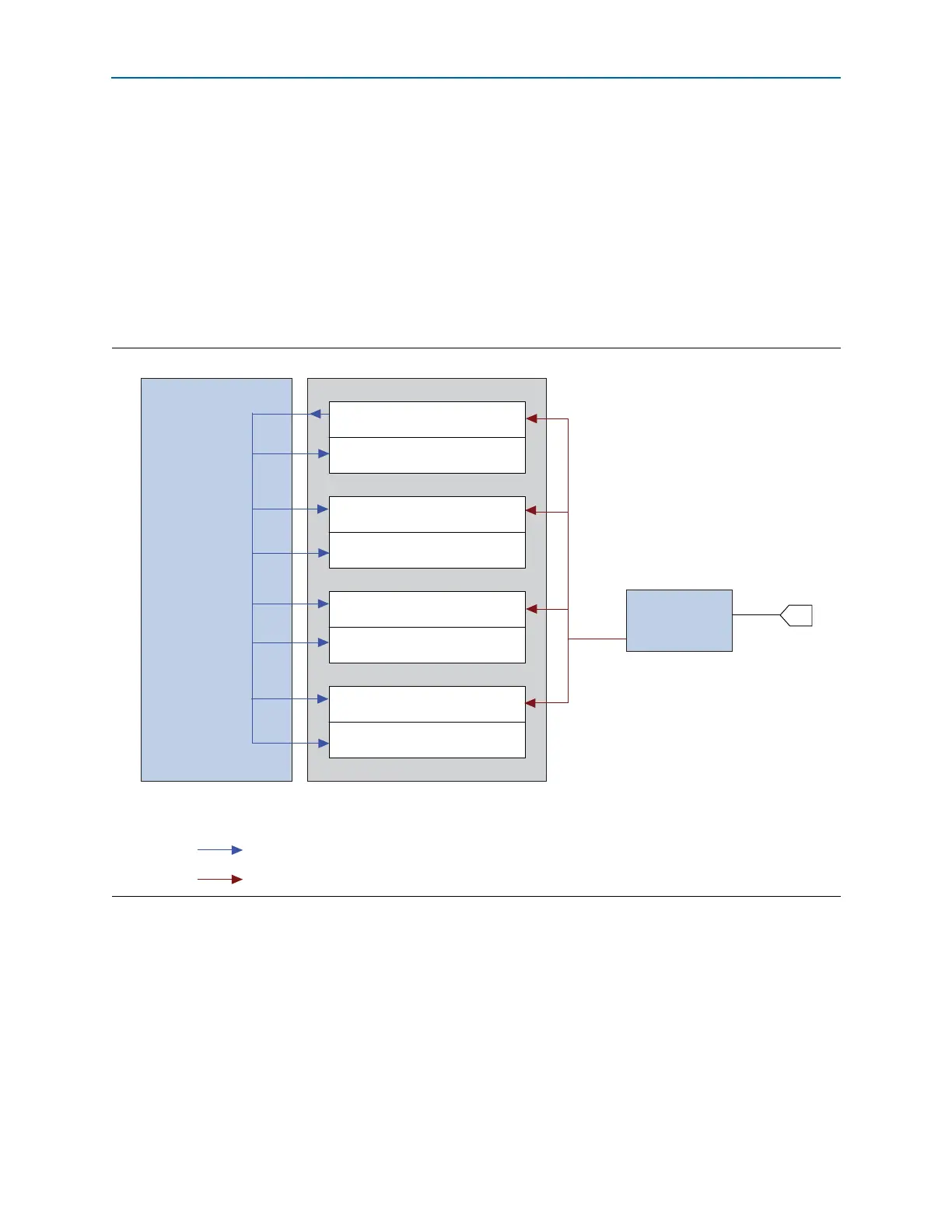

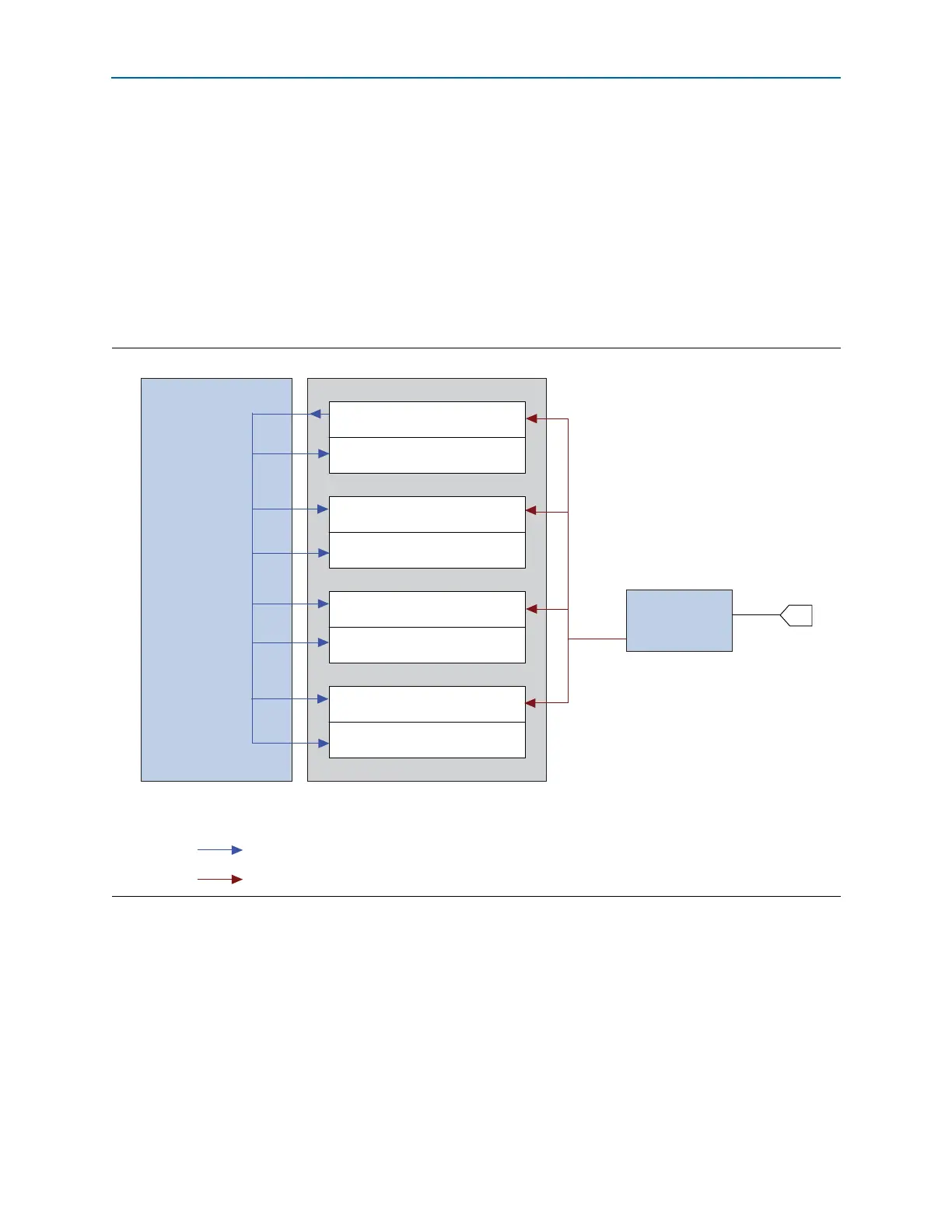

Option 1: Share a Single Transmitter Core Clock Between Receivers

■ Enable this option if you want

tx_clkout

of the first channel (channel 0) of the

transceiver block to provide the read clock to the Receive Phase Compensation

FIFOs of the remaining receiver channels in the transceiver block.

■ This option is typically enabled when all the channels of a transceiver block are in

a Basic or Protocol configuration with rate matching enabled and are reconfigured

to another Basic or Protocol configuration with rate matching enabled.

Figure 3–13 shows the sharing of channel 0’s

tx_clkout

between all four channels of a

transceiver block.

Figure 3–13. Option 1 for Receiver Core Clocking (Channel Reconfiguration Mode)

High-speed serial clock generated by the MPLL

Low-speed parallel clock (tx_clkout0)

FPGA Fabric Transceiver Block

tx_clkout[0]

TX0

RX0

TX1

TX2

TX3

RX1

RX2

RX3

MPLL

Loading...

Loading...