Chapter 3: Cyclone IV Dynamic Reconfiguration 3–35

Dynamic Reconfiguration Modes

November 2011 Altera Corporation Cyclone IV Device Handbook,

Volume 2

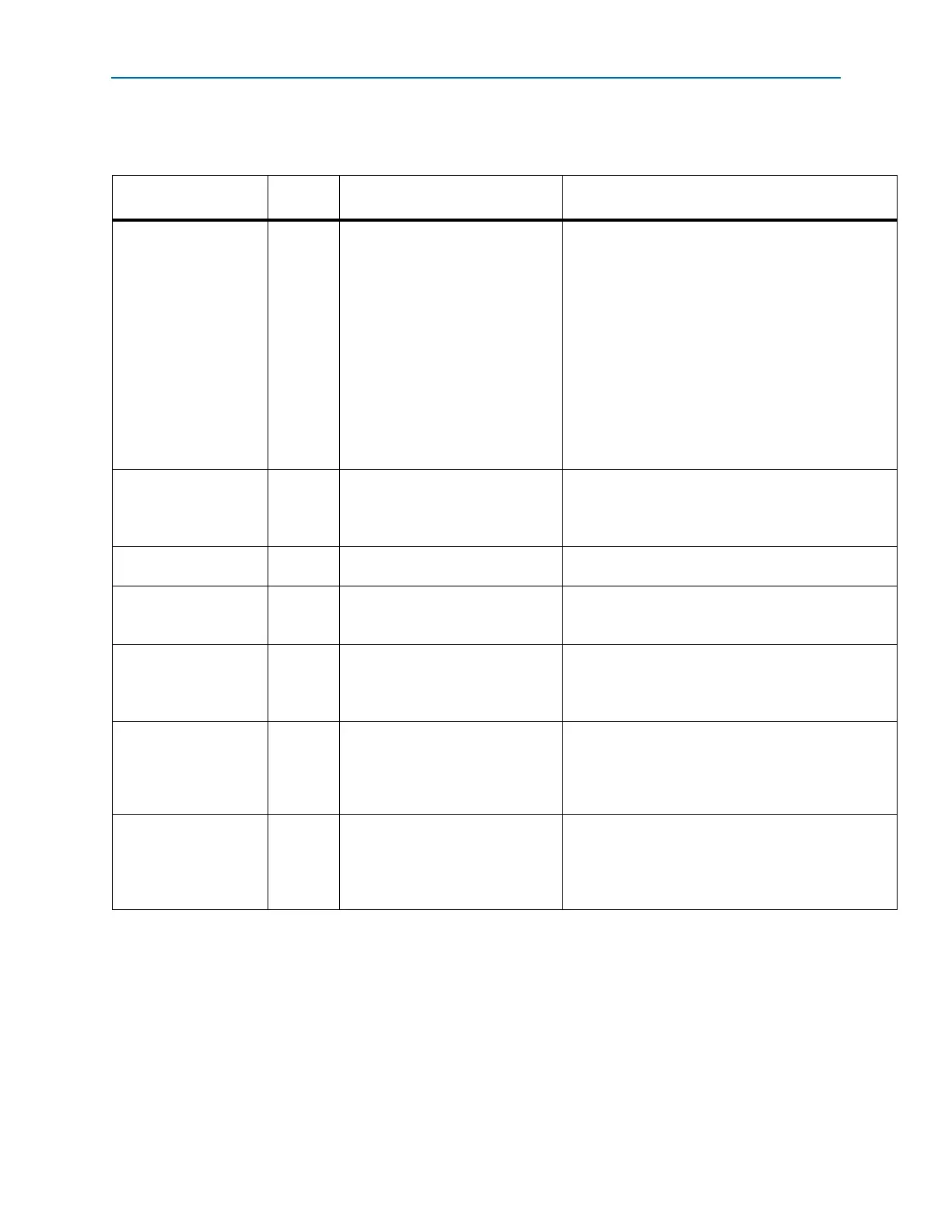

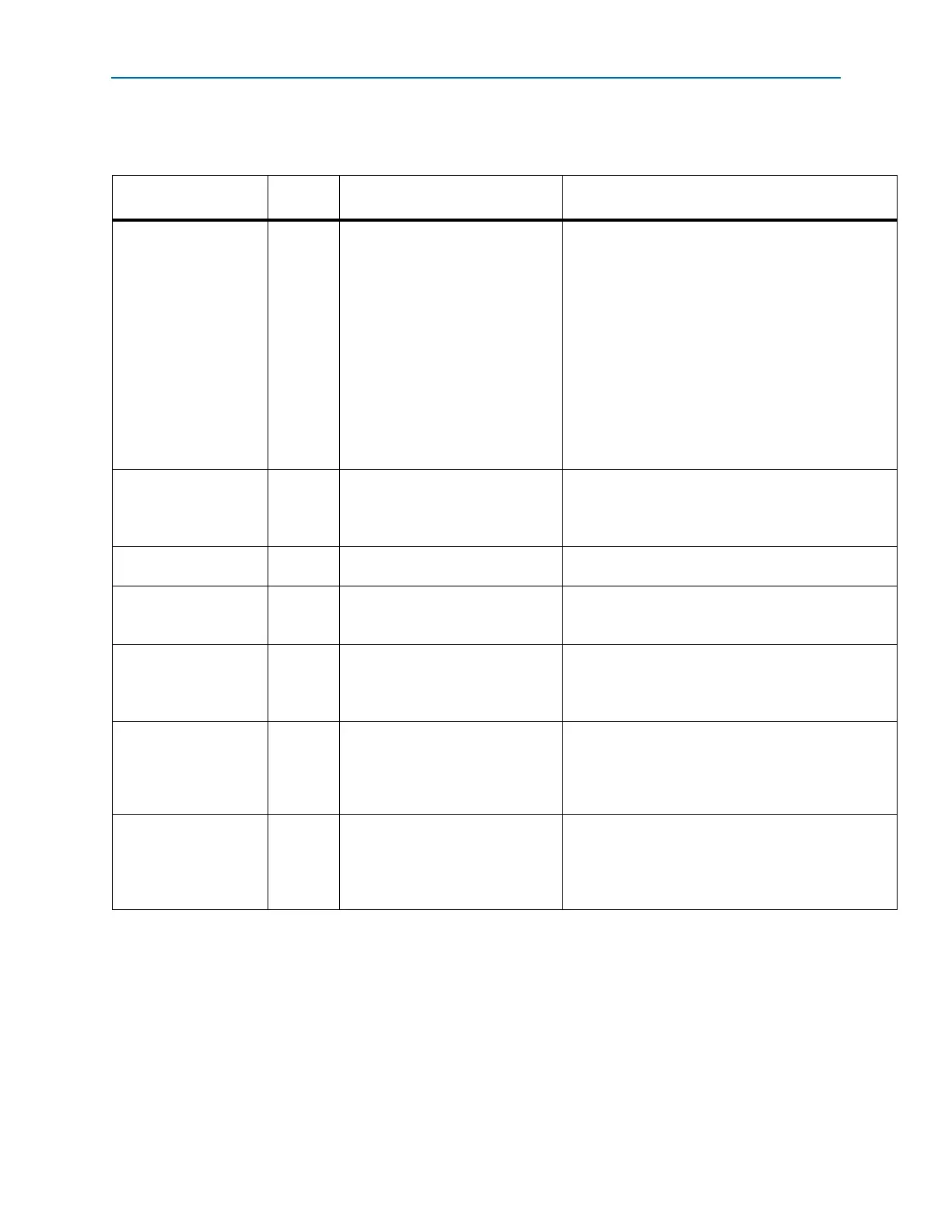

Table 3–7 lists the ALTGX megafunction ports for PLL Reconfiguration mode.

f For more information about the ALTPLL_RECONFIG megafunction port list,

description and usage, refer to the Phase-Locked Loop Reconfiguration

(ALTPL_RECONFIG) Megafunction User Guide.

Table 3–7. ALTGX Megafunction Port List for PLL Reconfiguration Mode

Port Name

(1)

Input/

Output

Description Comments

pll_areset [n..0]

Input

Resets the transceiver PLL. The

pll_areset

are asserted in two

conditions:

■ Used to reset the transceiver PLL

during the reset sequence. During

reset sequence, this signal is user

controlled.

■ After the transceiver PLL is

reconfigured, this signal is

asserted high by the

ALTPLL_RECONFIG controller. At

this time, this signal is not user

controlled.

You must connect the

pll_areset

port of ALTGX to the

pll_areset

port of the ALTPLL_RECONFIG

megafunction.

The ALTPLL_RECONFIG controller asserts the

pll_areset

port at the next rising clock edge after the

pll_reconfig_done

signal from the ALTGX

megafunction goes high. After the

pll_reconfig_done

signal goes high, the transceiver PLL is reset. When the

PLL reconfiguration is completed, this reset is

performed automatically by the ALTPLL_RECONFIG

megafunction and is not user controlled.

pll_scandata

[n..0]

Input

Receives the scan data input from

the ALTPLL_RECONFIG

megafunction.

The reconfigurable transceiver PLL received the scan

data input through this port for the dynamically

reconfigurable bits from the ALTPLL_RECONFIG

controller.

pll_scanclk

[n..0]

Input

Drives the

scanclk

port on the

reconfigurable transceiver PLL.

Connect the

pll_scanclk

port of the ALTGX

megafunction to the ALTPLL_RECONFIG

scanclk

port.

pll_scanclkena

[n..0]

Input

Acts as a clock enable for the

scanclk

port on the reconfigurable

transceiver PLL.

Connect the

pll_scanclkena

port of the ALTGX

megafunction to the ALTPLL_RECONFIG

scanclk

port.

pll_configupdate

[n..0]

Input

Drives the

configupdate

port on

the reconfigurable transceiver PLL.

This port is connected to the

pll_configupdate

port

from the ALTPLL_RECONFIG controller. After the final

data bit is sent out, the ALTPLL_RECONFIG controller

asserts this signal.

pll_reconfig_done[n..0] Output

This signal is asserted to indicate the

reconfiguration process is done.

Connect the pll_reconfig_done port to the

pll_scandone

port on the ALTPLL_RECONFIG

controller. The transceiver PLL

scandone

output signal

drives this port and determines when the PLL is

reconfigured.

pll_scandataout

[n..0]

Output

This port scan out the current

configuration of the transceiver PLL.

Connect the pll_scandataout port to the

pll_scandataout

port of the ALTPLL_RECONFIG

controller. This port reads the current configuration of

the transceiver PLL and send it to the

ALTPLL_RECONFIG megafunction.

Note to Table 3–7:

(1) <n> = (number of transceiver PLLs configured in the ALTGX MegaWizard) - 1.

Loading...

Loading...