3–10 Chapter 3: Memory Blocks in Cyclone IV Devices

Memory Modes

Cyclone IV Device Handbook, November 2011 Altera Corporation

Volume 1

In simple dual-port mode, M9K memory blocks support separate

wren

and

rden

signals. You can save power by keeping the

rden

signal low (inactive) when not

reading. Read-during-write operations to the same address can either output “Don’t

Care” data at that location or output “Old Data”. To choose the desired behavior, set

the Read-During-Write option to either Don’t Care or Old Data in the RAM

MegaWizard Plug-In Manager in the Quartus II software. For more information about

this behavior, refer to “Read-During-Write Operations” on page 3–15.

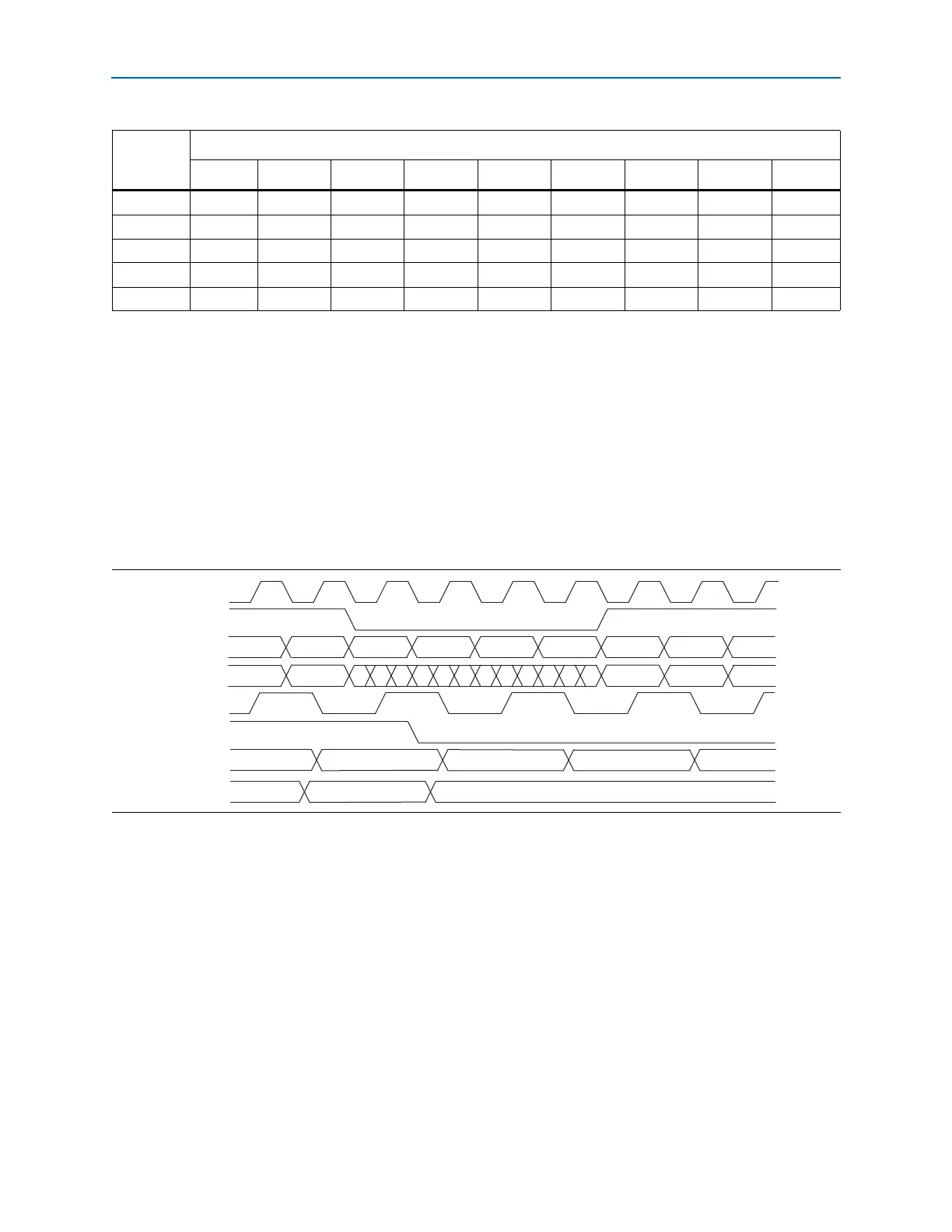

Figure 3–9 shows the timing waveform for read and write operations in simple

dual-port mode with unregistered outputs. Registering the outputs of the RAM

simply delays the

q

output by one clock cycle.

512 × 16 vvvvvv———

256 × 32 vvvvvv———

1024 × 9 — —————vvv

512×18——————vvv

256×36——————vvv

Table 3–3. Cyclone IV Devices M9K Block Mixed-Width Configurations (Simple Dual-Port Mode) (Part 2 of 2)

Read Port

Write Port

8192

× 14096× 2 2048 × 4 1024 × 8 512 × 16 256 × 32 1024 × 9512× 18 256 × 36

Figure 3–9. Cyclone IV Devices Simple Dual-Port Timing Waveform

wrclock

wren

wraddress

rdclock

an-1

an

a0 a1 a2 a3 a4 a5

a6

q (asynch)

rden

rdaddress

bn

b0

b1 b2 b3

doutn-1 doutn

dout0

din-1 din din4 din5 din6

data

Loading...

Loading...