Chapter 5: Clock Networks and PLLs in Cyclone IV Devices 5–9

Clock Networks

October 2012 Altera Corporation Cyclone IV Device Handbook,

Volume 1

DPCLK2

(4)

CDPCLK1

, or

CDPCLK2

(2),

(5)

———vv———————————————

DPCLK5

(4)

DPCLK7

(2)

—————v ——————————————

DPCLK4

(4)

DPCLK6

(2)

——————v —————————————

DPCLK6

(4)

CDPCLK5

, or

CDPCLK6

(2),

(5)

———————v ————————————

DPCLK3

(4)

CDPCLK4

, or

CDPCLK3

(2),

(5)

————————vv——————————

DPCLK8

——————————v —————————

DPCLK11

———————————v ————————

DPCLK9

————————————v ———————

DPCLK10

—————————————vv—————

DPCLK5

———————————————v ————

DPCLK2

————————————————v ———

DPCLK4

—————————————————v ——

DPCLK3

——————————————————vv

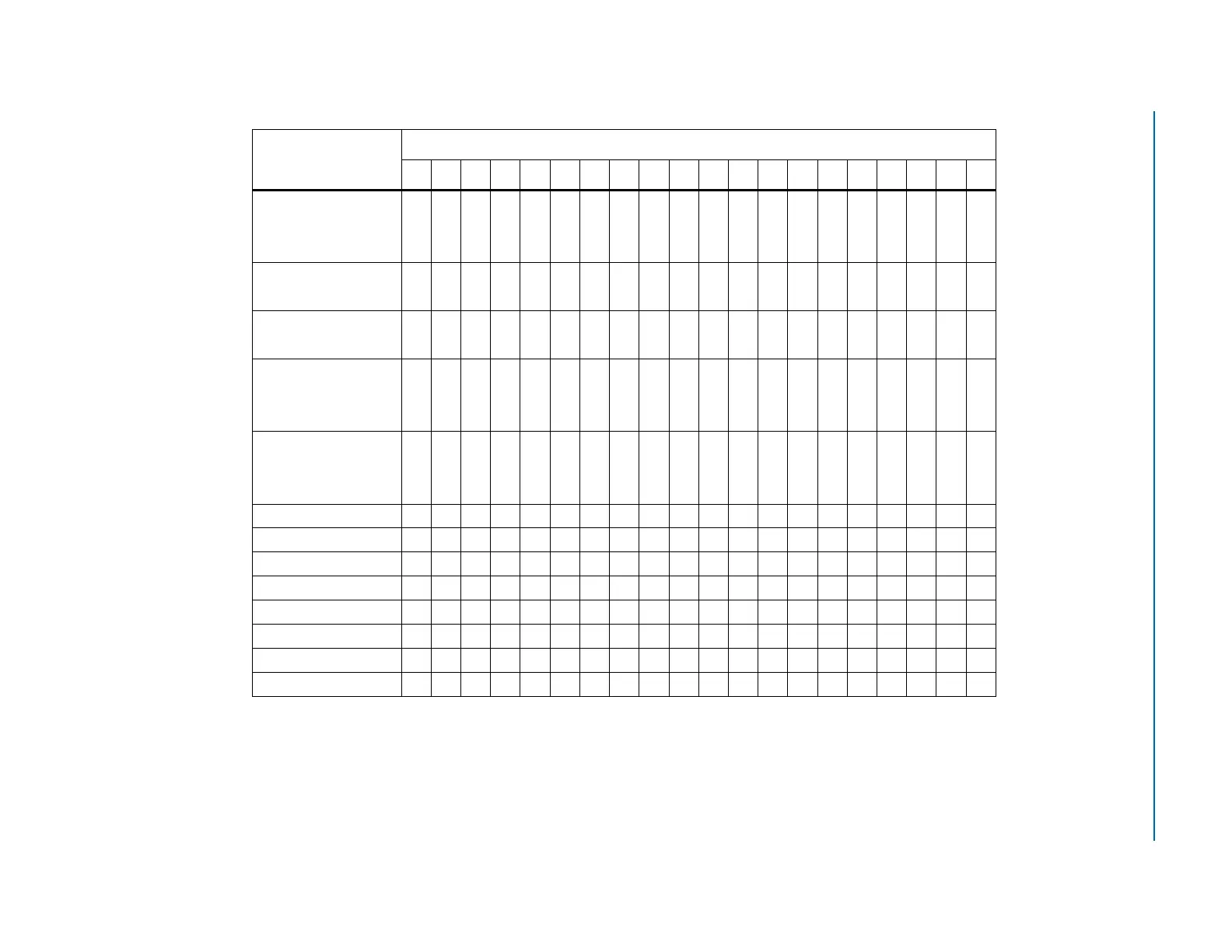

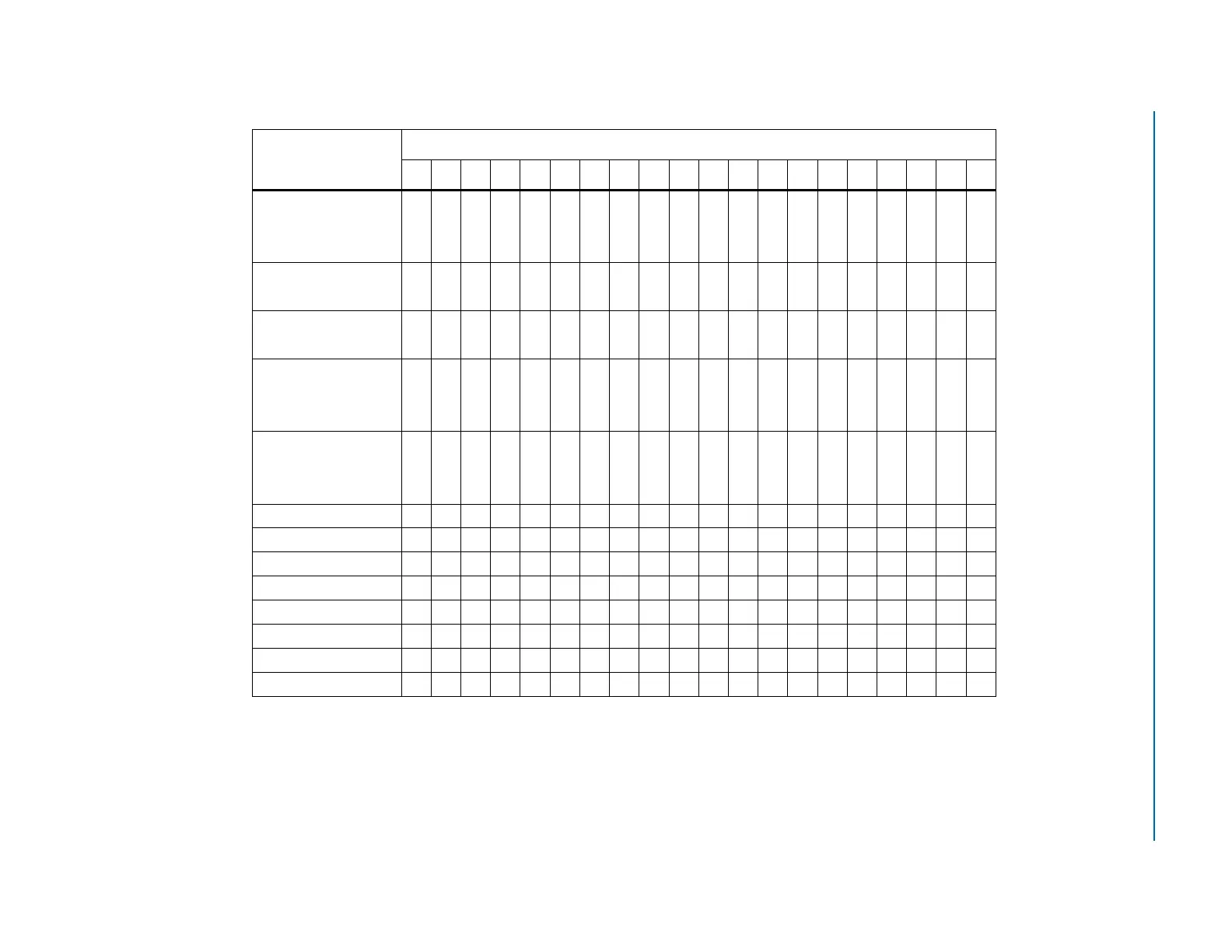

Notes to Table 5–3:

(1) EP4CE6 and EP4CE10 devices only have GCLK networks 0 to 9.

(2) These pins apply to all Cyclone IV E devices except EP4CE6 and EP4CE10 devices.

(3) EP4CE6 and EP4CE10 devices only have

PLL_1

and

PLL_2

.

(4) This pin applies only to EP4CE6 and EP4CE10 devices.

(5) Only one of the two

CDPCLK

pins can feed the clock control block. You can use the other pin as a regular I/O pin.

Table 5–3. GCLK Network Connections for Cyclone IV E Devices

(1)

(Part 3 of 3)

GCLK Network Clock

Sources

GCLK Networks

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

Loading...

Loading...