Chapter 5: Clock Networks and PLLs in Cyclone IV Devices 5–19

PLLs in Cyclone IV Devices

October 2012 Altera Corporation Cyclone IV Device Handbook,

Volume 1

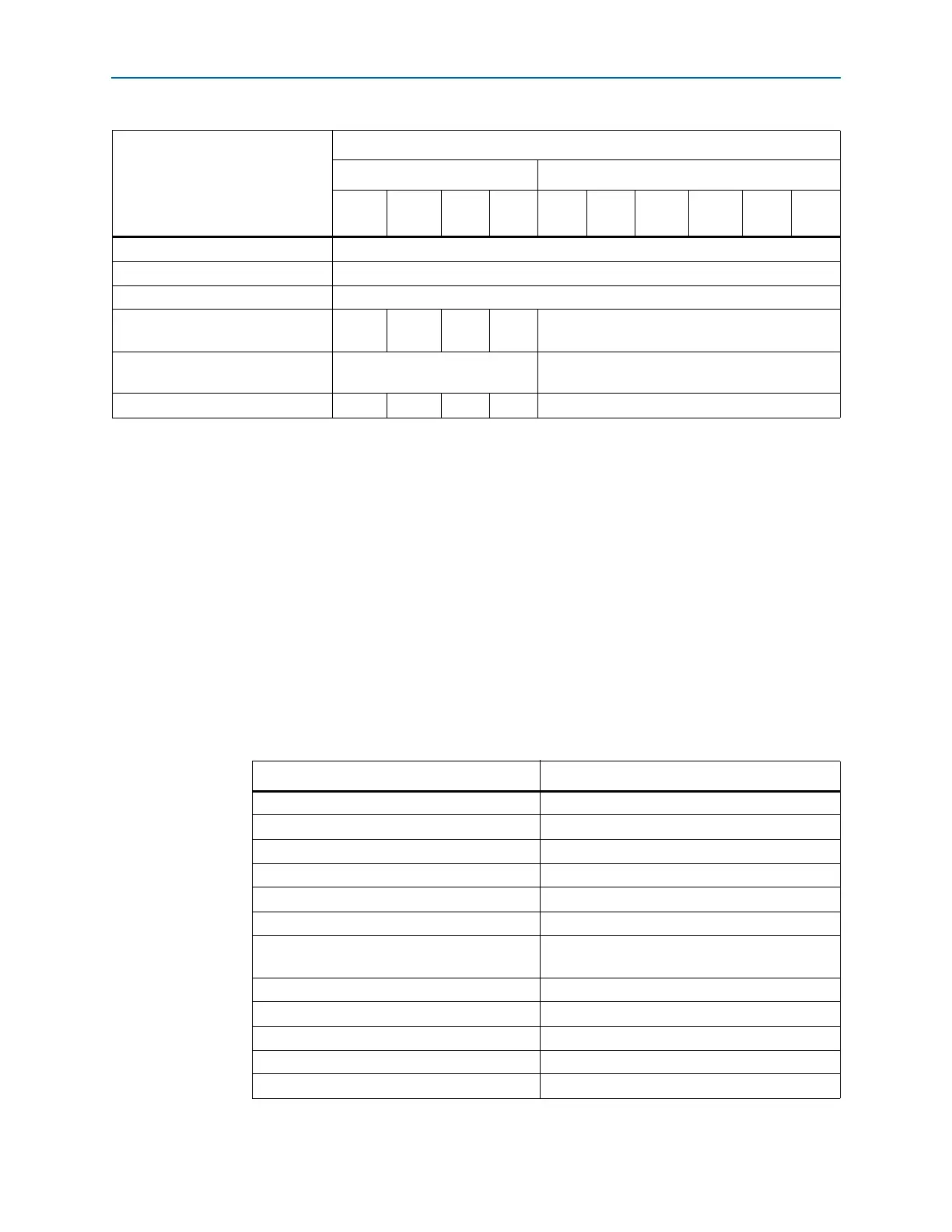

Tab le 5 –6 lists the features available in Cyclone IV E PLLs.

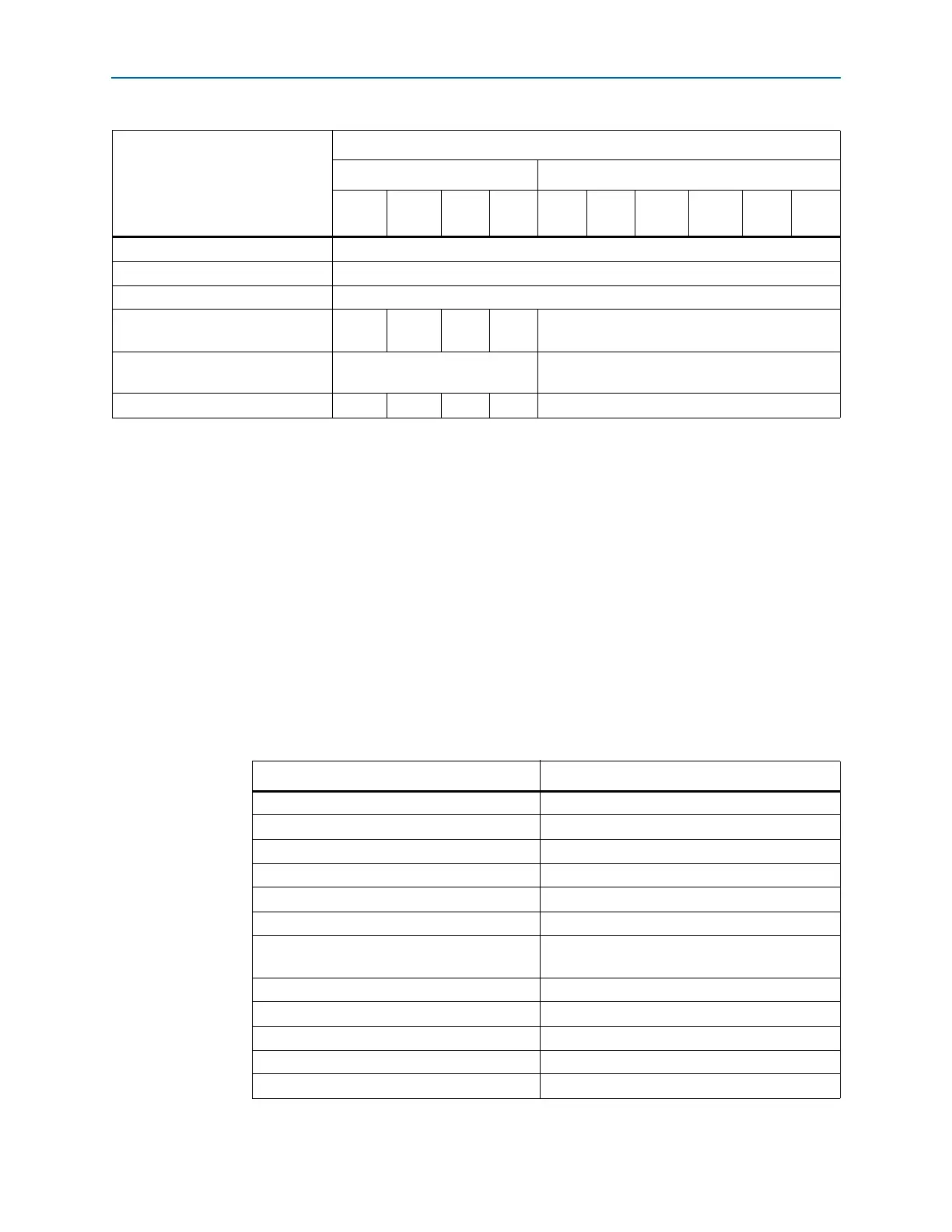

Input clock switchover v

User mode reconfiguration v

Loss of lock detection v

PLL drives TX Serial Clock, TX Load

Enable, and TX Parallel Clock

vv—— v

VCO output drives RX clock data

recovery (CDR) clock

— v

PLL drives

FREF

for ppm detect vv—— v

Notes to Table 5–5:

(1) This is only applicable to EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices in F672 and F896 package.

(2) This is applicable to all Cyclone IV devices.

(3) This is applicable to all Cyclone IV devices except EP4CGX15 devices in all packages, EP4CGX22, and EP4CGX30 devices in F169 package.

(4) This is only applicable to EP4CGX15, EP4CGX22, and all EP4CGX30 devices except EP4CGX30 in the F484 package..

(5) C counters range from 1 through 512 if the output clock uses a 50% duty cycle. For any output clocks using a non-50% duty cycle, the

post

-scale counters range from 1 through 256.

(6) These clock pins can access the GCLK networks.

(7) These clock pins are only available in EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices and cannot access the GCLK networks.

CLK[17,19,20,21]p

can be used as single-ended clock input pins.

(8) Only applicable if the input clock jitter is in the input jitter tolerance specifications.

(9) The smallest phase shift is determined by the voltage

-controlled oscillator (VCO) period divided by eight. For degree increments, Cyclone IV GX

devices can shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and

divide parameters.

(10) This is applicable to the EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices in F484 package.

Table 5–5. Cyclone IV GX PLL Features (Part 2 of 2)

Features

Availability

General Purpose PLLs Multipurpose PLLs

PLL_1

(1), (10)

PLL_2

(1), (10)

PLL_

3

(2)

PLL_

4

(3)

PLL_1

(4)

PLL_2

(4)

PLL_5

(1), (10)

PLL_6

(1), (10)

PLL_7

(1)

PLL_8

(1)

Table 5–6. Cyclone IV E PLL Features (Part 1 of 2)

Hardware Features Availability

C (output counters) 5

M, N, C counter sizes 1 to 512

(1)

Dedicated clock outputs 1 single-ended or 1 differential pair

Clock input pins 4 single-ended or 2 differential pairs

Spread-spectrum input clock tracking v

(2)

PLL cascading Through GCLK

Compensation modes

Source-Synchronous Mode, No Compensation

Mode, Normal Mode, and Zero Delay Buffer Mode

Phase shift resolution Down to 96-ps increments

(3)

Programmable duty cycle v

Output counter cascading v

Input clock switchover v

User mode reconfiguration v

Loading...

Loading...