Port Integration Module (S12GPIMV1)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 235

2.4.3.57 Port AD Pull Enable Register (PER0AD)

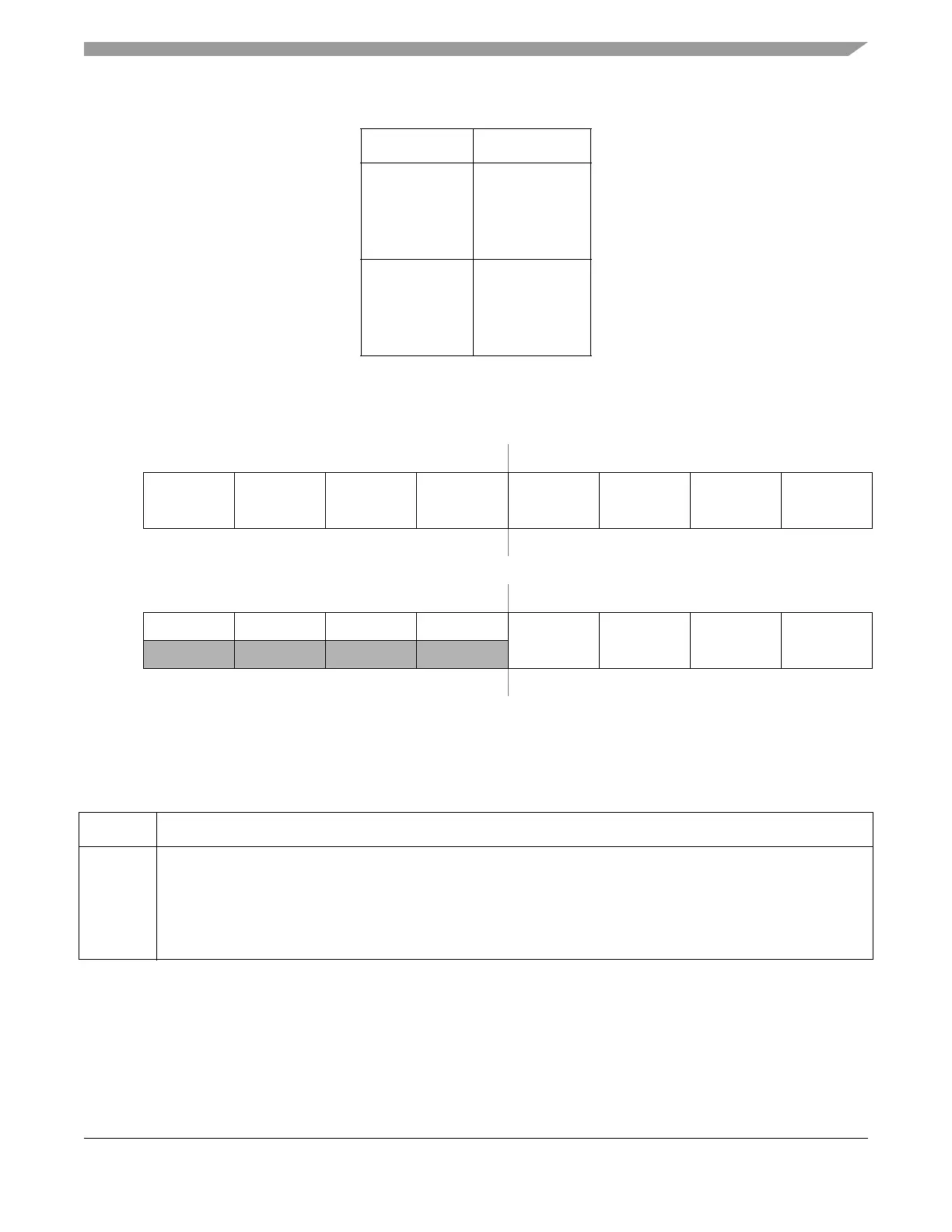

Table 2-82. AN Routing Options

PRR1AN Associated Pins

0 AN10 - PAD10

AN11 - PAD11

AN13 - PAD13

AN14 - PAD14

AN15 - PAD15

1 AN10 - PC0

AN11 - PC1

AN13 - PC2

AN14 - PC3

AN15 - PC4

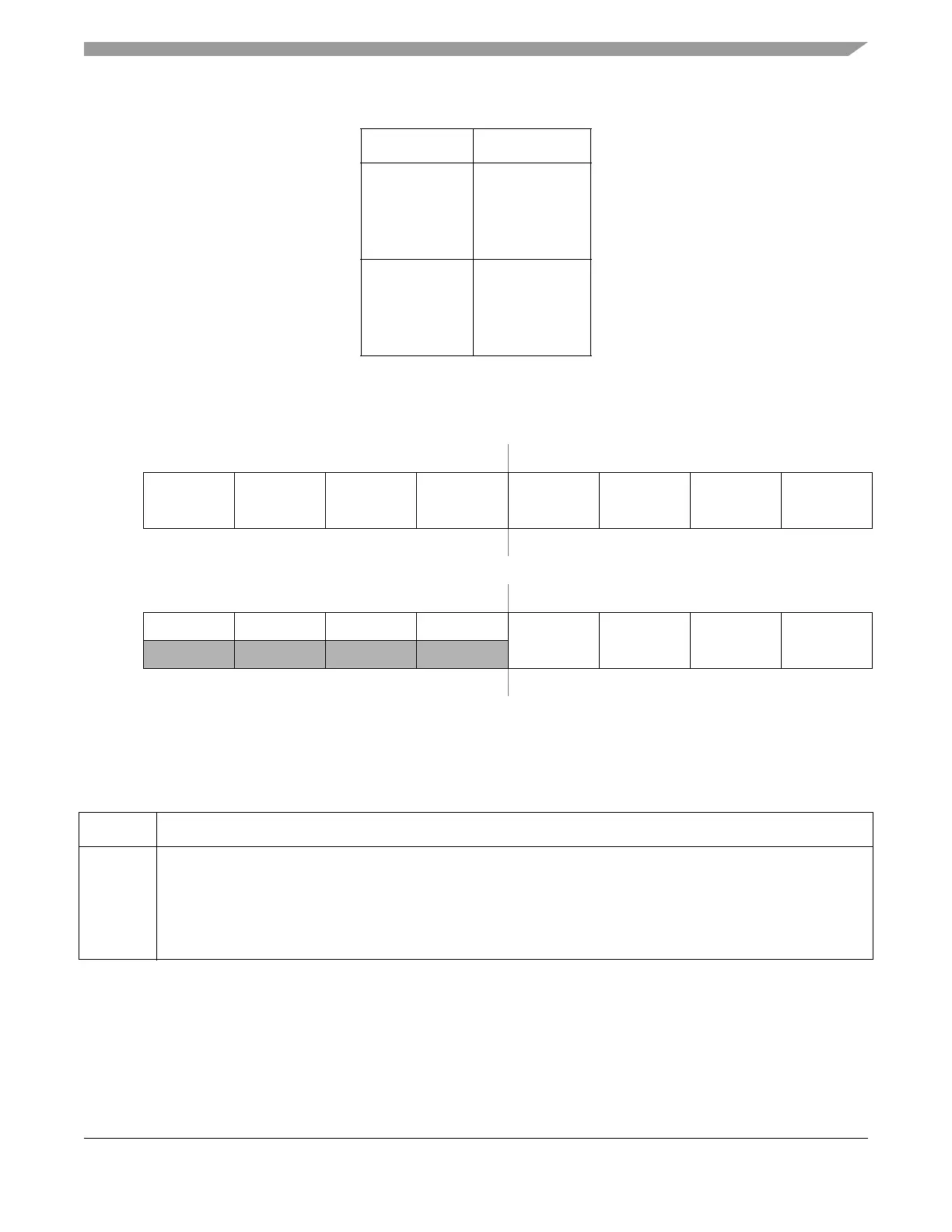

Address 0x0278 (G1, G2) Access: User read/write

1

1

Read: Anytime

Write: Anytime

76543210

R

PER0AD7 PER0AD6 PER0AD5 PER0AD4 PER0AD3 PER0AD2 PER0AD1 PER0AD0

W

Reset00000000

Address 0x0278 (G3) Access: User read/write

1

76543210

R0000

PER0AD3 PER0AD2 PER0AD1 PER0AD0

W

Reset00000000

Figure 2-56. Port AD Pullup Enable Register (PER0AD)

Table 2-83. PER0AD Register Field Descriptions

Field Description

7-0

PER0AD

Port AD pull enable—Enable pull device on input pin

This bit controls whether a pull device on the associated port input pin is active. If a pin is used as output this bit has

no effect. The polarity is selected by the related polarity select register bit.

1 Pull device enabled

0 Pull device disabled

Loading...

Loading...