Scalable Controller Area Network (S12MSCANV3)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 611

18.4.3.1 Protocol Violation Protection

The MSCAN protects the user from accidentally violating the CAN protocol through programming errors.

The protection logic implements the following features:

• The receive and transmit error counters cannot be written or otherwise manipulated.

• All registers which control the configuration of the MSCAN cannot be modified while the MSCAN

is on-line. The MSCAN has to be in Initialization Mode. The corresponding INITRQ/INITAK

handshake bits in the CANCTL0/CANCTL1 registers (see Section 18.3.2.1, “MSCAN Control

Register 0 (CANCTL0)”) serve as a lock to protect the following registers:

— MSCAN control 1 register (CANCTL1)

— MSCAN bus timing registers 0 and 1 (CANBTR0, CANBTR1)

— MSCAN identifier acceptance control register (CANIDAC)

— MSCAN identifier acceptance registers (CANIDAR0–CANIDAR7)

— MSCAN identifier mask registers (CANIDMR0–CANIDMR7)

• The TXCAN is immediately forced to a recessive state when the MSCAN goes into the power

down mode or initialization mode (see Section 18.4.5.6, “MSCAN Power Down Mode,” and

Section 18.4.4.5, “MSCAN Initialization Mode”).

• The MSCAN enable bit (CANE) is writable only once in normal system operation modes, which

provides further protection against inadvertently disabling the MSCAN.

18.4.3.2 Clock System

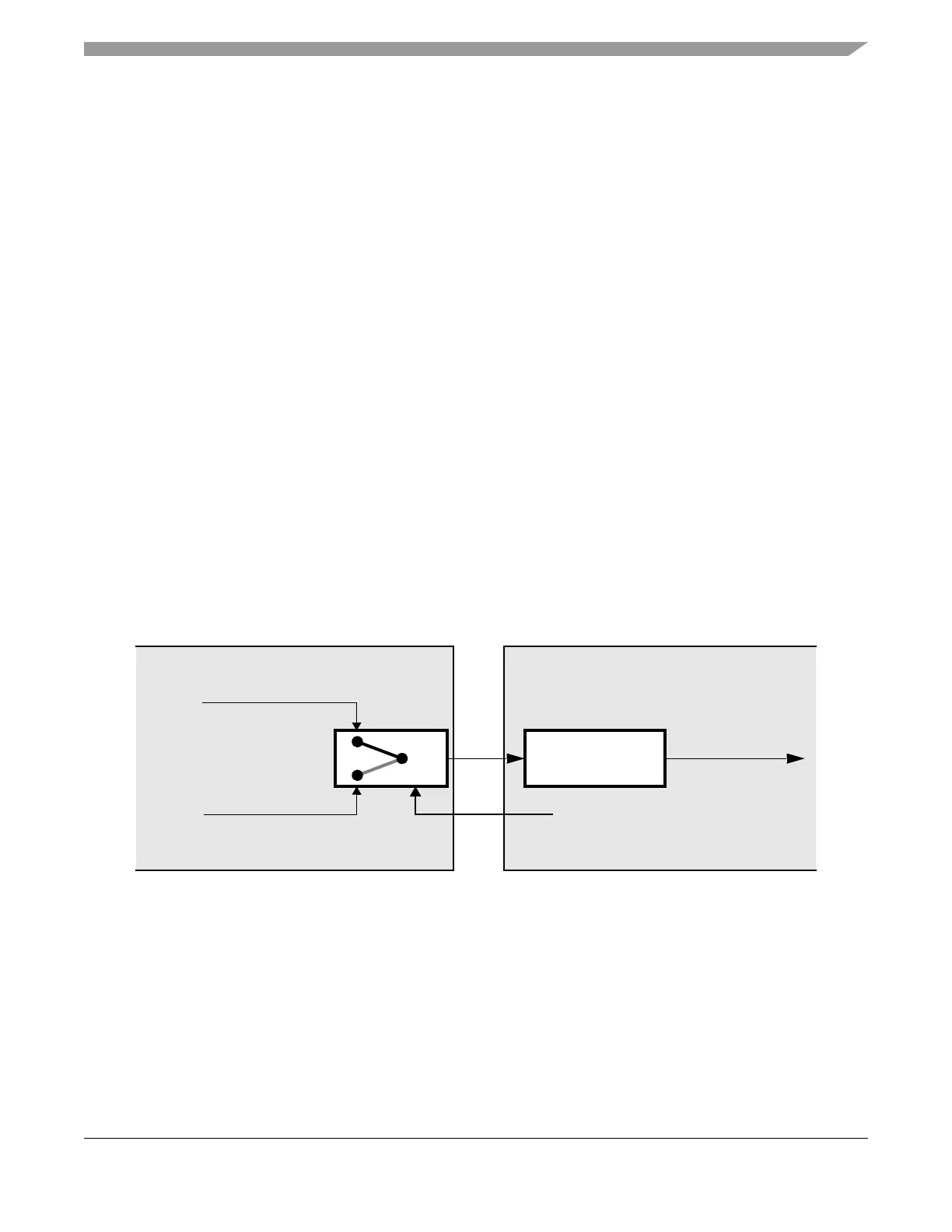

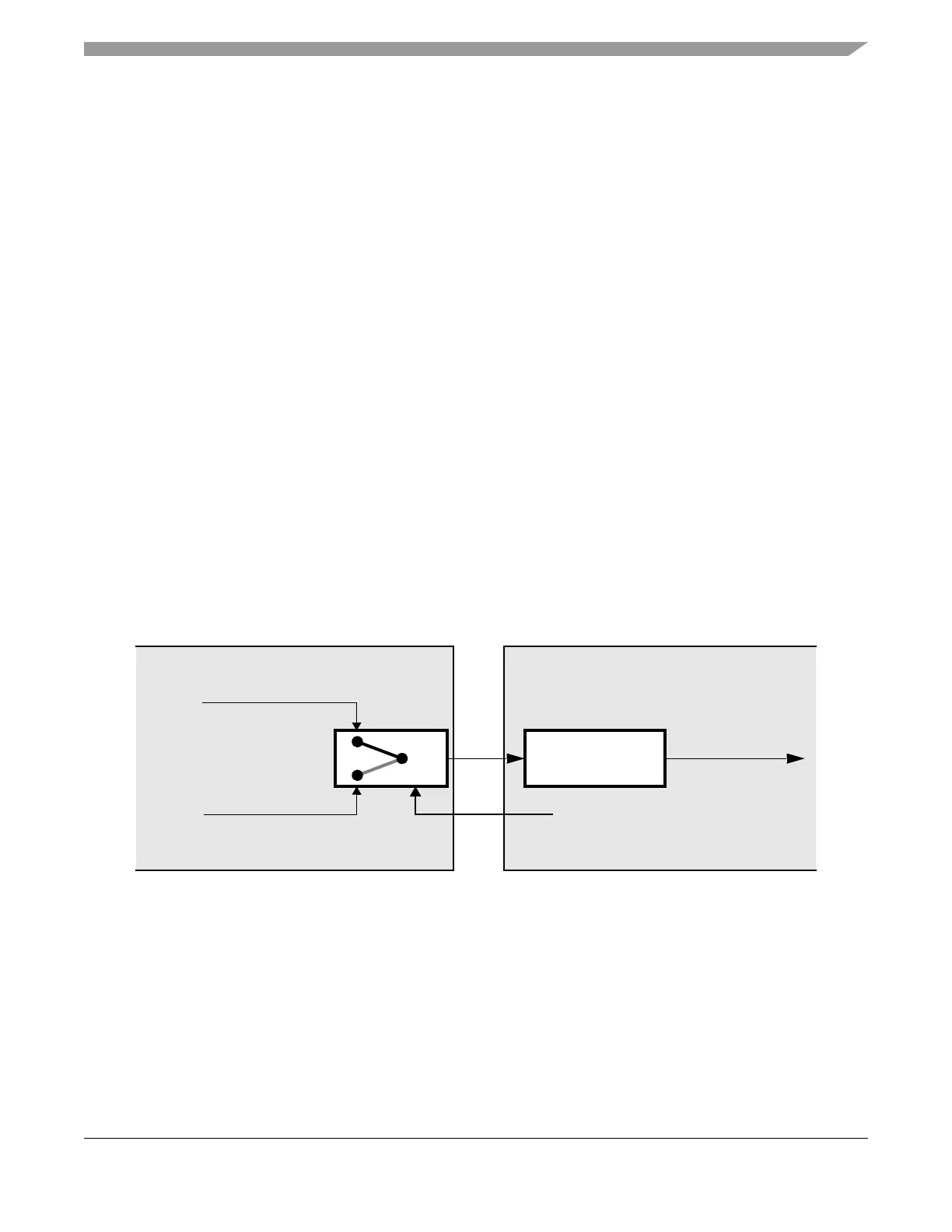

Figure 18-43 shows the structure of the MSCAN clock generation circuitry.

Figure 18-43. MSCAN Clocking Scheme

The clock source bit (CLKSRC) in the CANCTL1 register (18.3.2.2/18-576) defines whether the internal

CANCLK is connected to the output of a crystal oscillator (oscillator clock) or to the bus clock.

The clock source has to be chosen such that the tight oscillator tolerance requirements (up to 0.4%) of the

CAN protocol are met. Additionally, for high CAN bus rates (1 Mbps), a 45% to 55% duty cycle of the

clock is required.

If the bus clock is generated from a PLL, it is recommended to select the oscillator clock rather than the

bus clock due to jitter considerations, especially at the faster CAN bus rates.

Bus Clock

Oscillator Clock

MSCAN

CANCLK

CLKSRC

CLKSRC

Prescaler

(1 .. 64)

Time quanta clock (Tq)

Loading...

Loading...