Serial Peripheral Interface (S12SPIV5)

MC9S12G Family Reference Manual Rev.1.27

700 NXP Semiconductors

21.3.2.4 SPI Status Register (SPISR)

Read: Anytime

Write: Has no effect

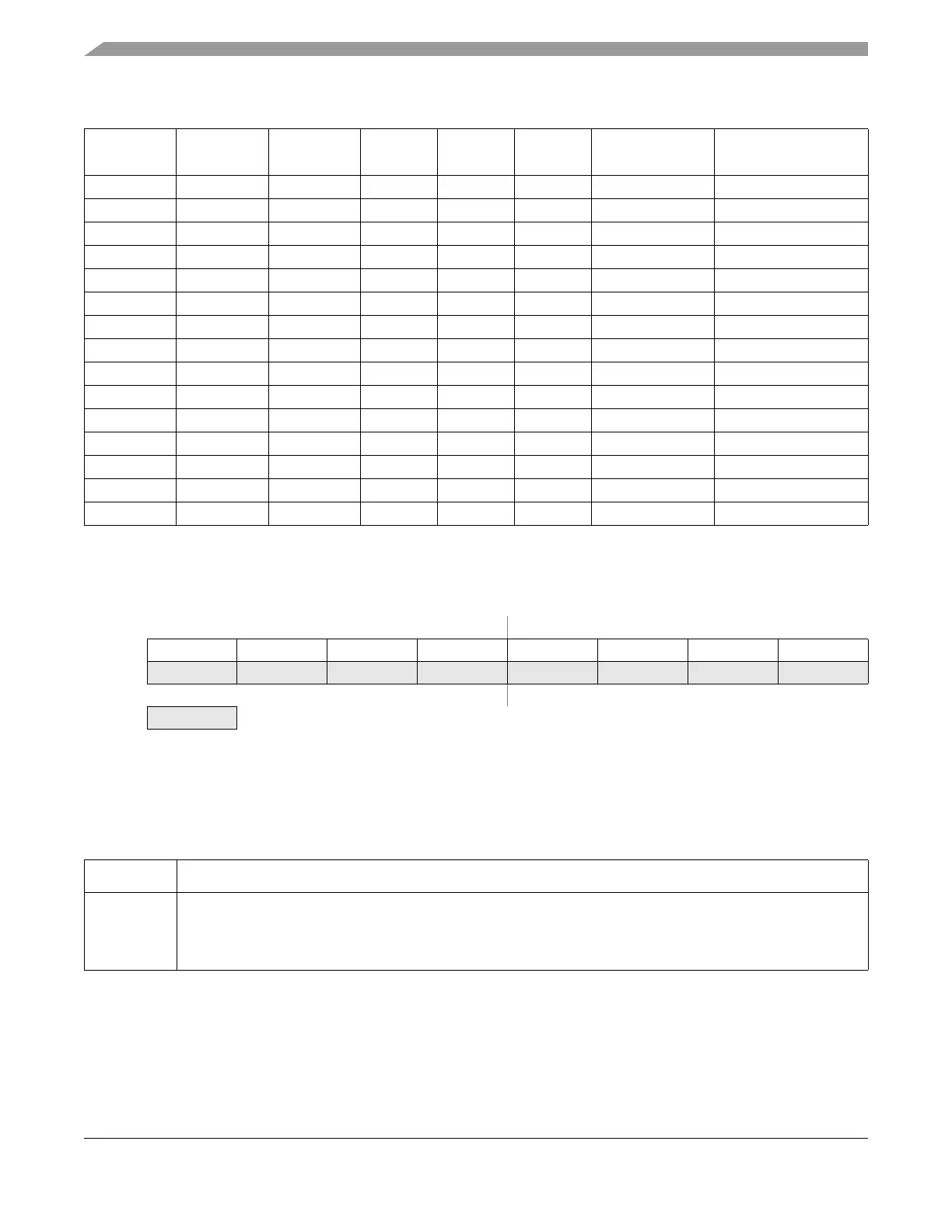

1 1 0 0 0 1 28 892.86 kbit/s

1 1 0 0 1 0 56 446.43 kbit/s

1 1 0 0 1 1 112 223.21 kbit/s

1 1 0 1 0 0 224 111.61 kbit/s

1 1 0 1 0 1 448 55.80 kbit/s

1 1 0 1 1 0 896 27.90 kbit/s

1 1 0 1 1 1 1792 13.95 kbit/s

1 1 1 0 0 0 16 1.5625 Mbit/s

1 1 1 0 0 1 32 781.25 kbit/s

1 1 1 0 1 0 64 390.63 kbit/s

1 1 1 0 1 1 128 195.31 kbit/s

1 1 1 1 0 0 256 97.66 kbit/s

1 1 1 1 0 1 512 48.83 kbit/s

1 1 1 1 1 0 1024 24.41 kbit/s

1 1 1 1 1 1 2048 12.21 kbit/s

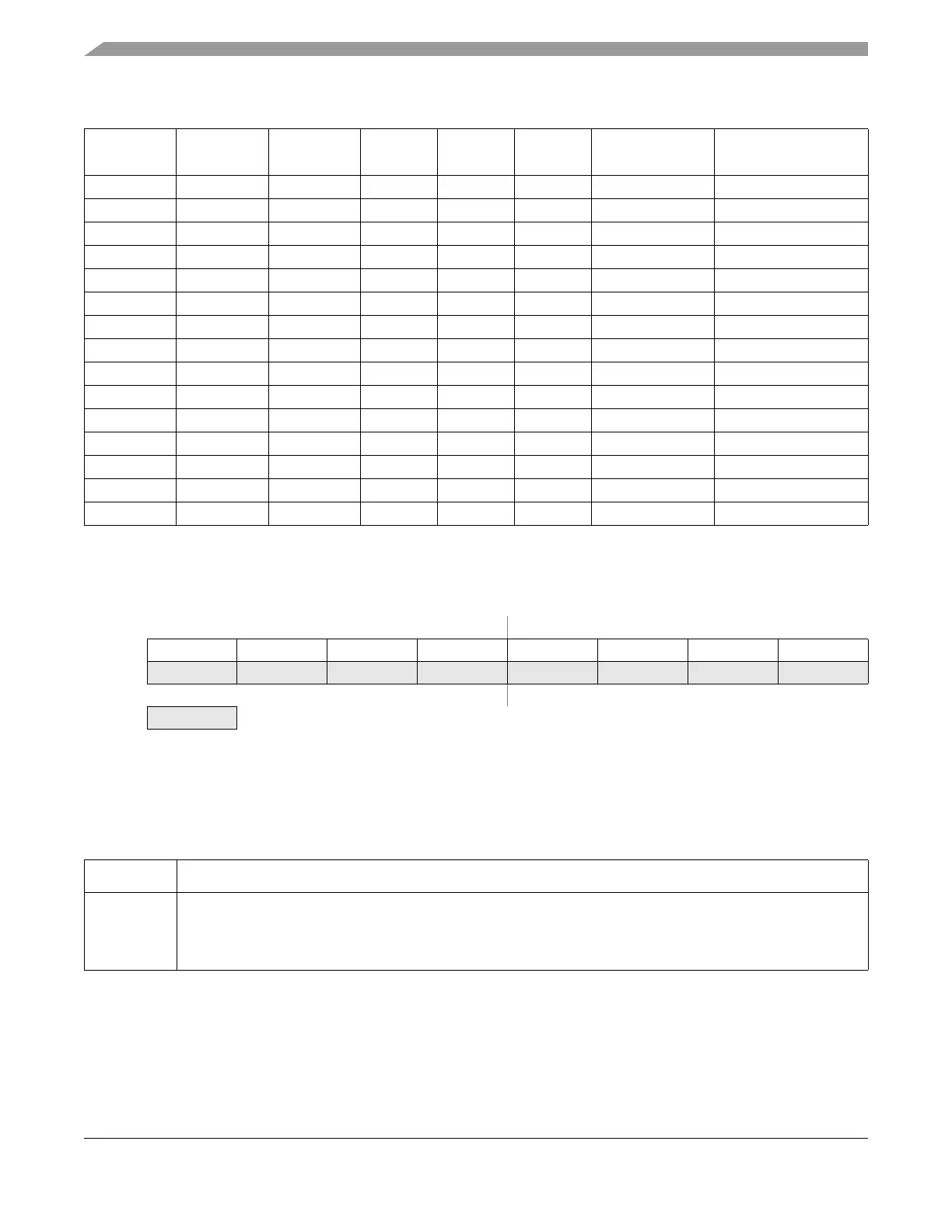

Module Base +0x0003

76543210

R SPIF 0 SPTEF MODF 0 0 0 0

W

Reset00100000

= Unimplemented or Reserved

Figure 21-6. SPI Status Register (SPISR)

Table 21-7. SPISR Field Descriptions

Field Description

7

SPIF

SPIF Interrupt Flag — This bit is set after received data has been transferred into the SPI data register. For

information about clearing SPIF Flag, please refer to Table 21-8.

0 Transfer not yet complete.

1 New data copied to SPIDR.

Table 21-6. Example SPI Baud Rate Selection (25 MHz Bus Clock)

SPPR2 SPPR1 SPPR0 SPR2 SPR1 SPR0

Baud Rate

Divisor

Baud Rate

Loading...

Loading...