Timer Module (TIM16B6CV3)

MC9S12G Family Reference Manual Rev.1.27

726 NXP Semiconductors

22.3.2.6 Timer Control Register 1/Timer Control Register 2 (TCTL1/TCTL2)

Read: Anytime

Write: Anytime

Table 22-5. TTOV Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

Field Description

5:0

TOV[5:0]

Toggle On Overflow Bits — TOVx toggles output compare pin on overflow. This feature only takes effect when

in output compare mode. When set, it takes precedence over forced output compare

0 Toggle output compare pin on overflow feature disabled.

1 Toggle output compare pin on overflow feature enabled.

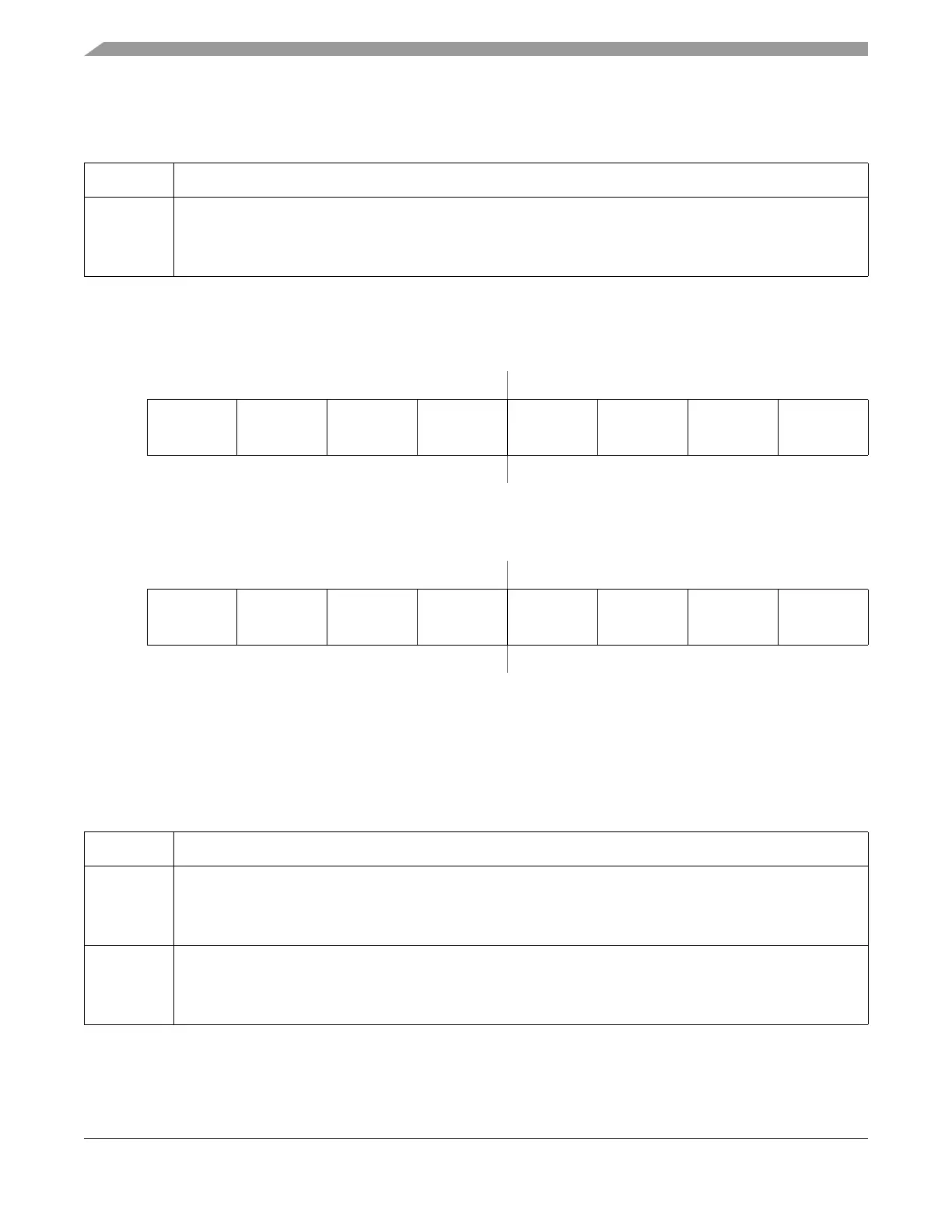

Module Base + 0x0008

76543210

R

RESERVED RESERVED RESERVED RESERVED OM5 OL5 OM4 OL4

W

Reset00000000

Figure 22-10. Timer Control Register 1 (TCTL1)

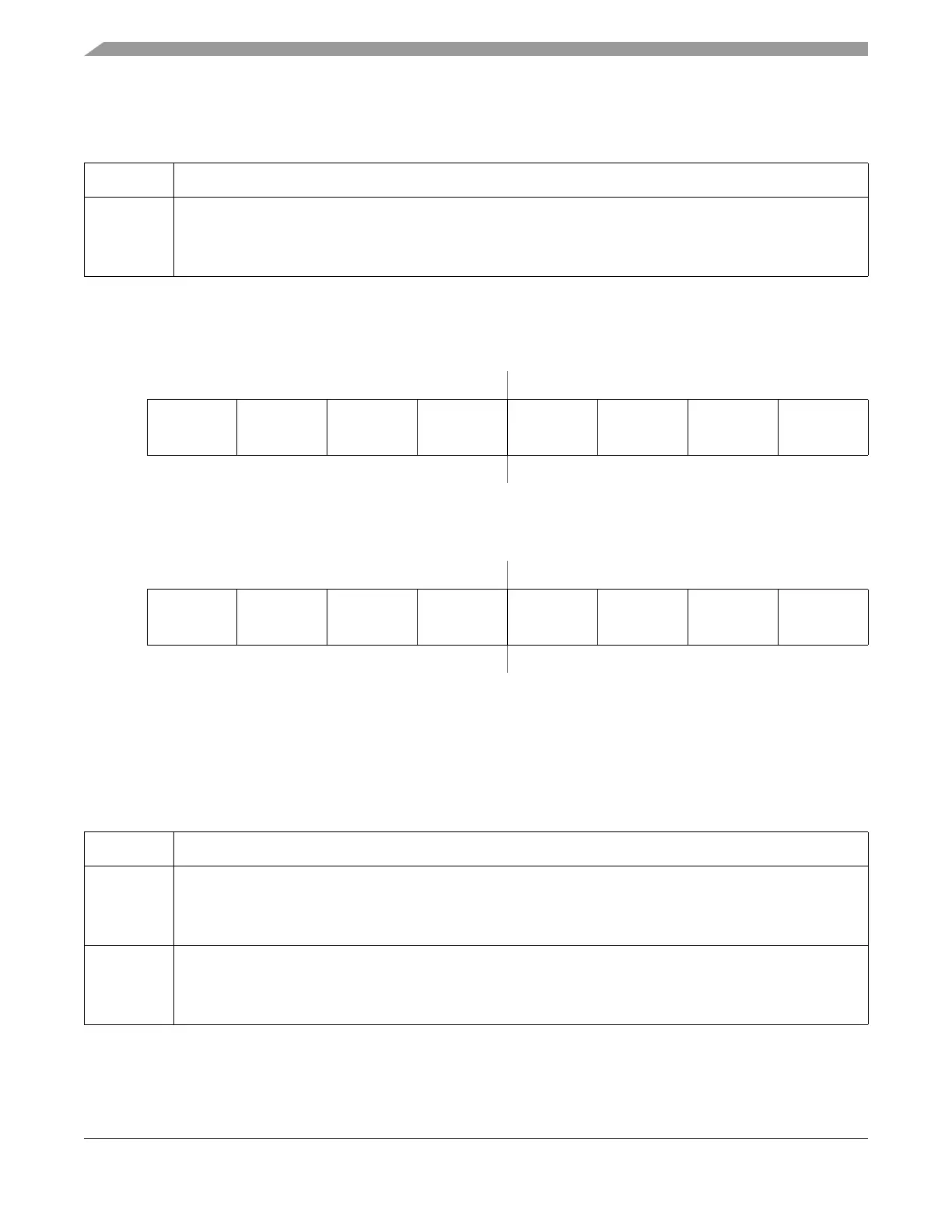

Module Base + 0x0009

76543210

R

OM3 OL3 OM2 OL2 OM1 OL1 OM0 OL0

W

Reset00000000

Figure 22-11. Timer Control Register 2 (TCTL2)

Table 22-6. TCTL1/TCTL2 Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero

Field Description

5:0

OMx

Output Mode — These six pairs of control bits are encoded to specify the output action to be taken as a result

of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output

tied to OCx.

Note: For an output line to be driven by an OCx the OCPDx must be cleared.

5:0

OLx

Output Level — These sixpairs of control bits are encoded to specify the output action to be taken as a result of

a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied

to OCx.

Note: For an output line to be driven by an OCx the OCPDx must be cleared.

Loading...

Loading...