RL78/G15 CHAPTER 6 TIMER ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 210 of 765

Mar 7, 2023

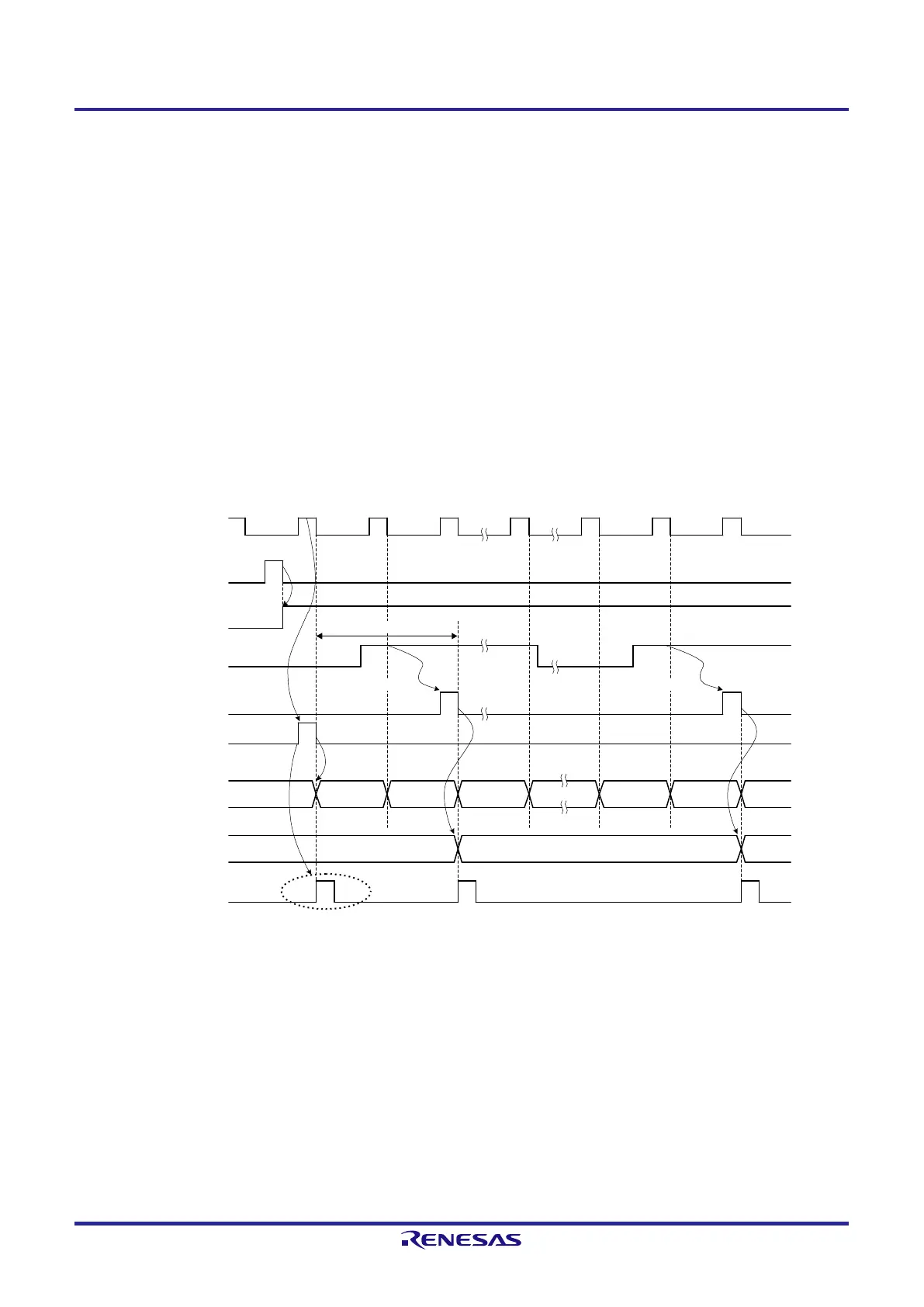

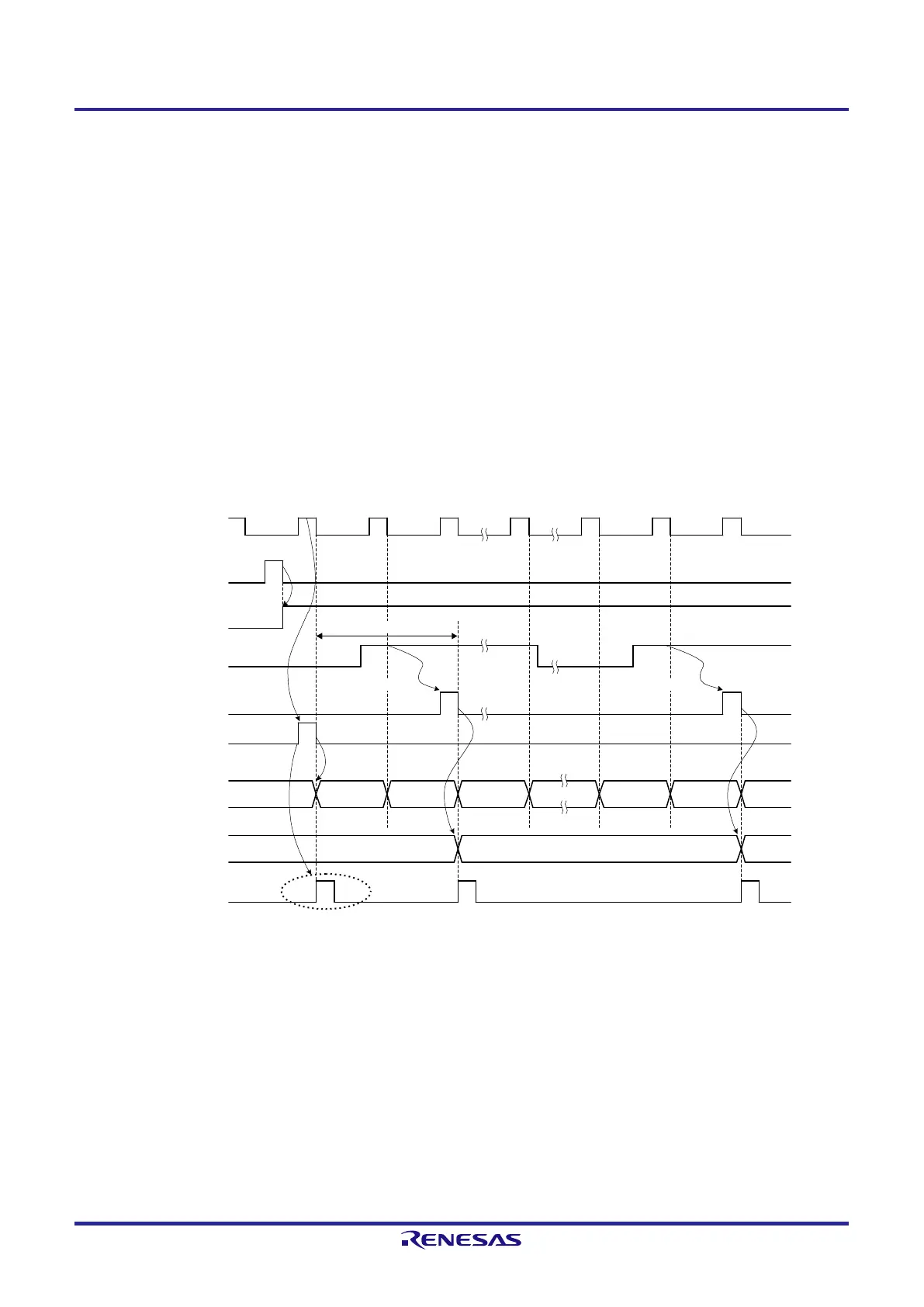

(3) Operation of capture mode (input pulse interval measurement)

<1> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit.

<2> Timer count register mn (TCRmn) holds the initial value until count clock generation.

<3> A start trigger is generated at the first count clock (f

MCK

) after operation is enabled. And the value of 0000H is

loaded to the TCRmn register and counting starts in the capture mode (When the MDmn0 bit is set to 1,

INTTMmn is generated by the start trigger).

<4> On detection of the valid edge of the TImn input, the value of the TCRmn register is captured to timer data

register mn (TDRmn) and an INTTMmn interrupt is generated. However, this capture value is nomeaning. The

TCRmn register keeps on counting from 0000H.

<5> On next detection of the valid edge of the TImn input, the value of the TCRmn register is captured to the TDRmn

register and an INTTMmn interrupt is generated.

Figure 6-26. Operation Timing (In Capture Mode: Input Pulse Interval Measurement)

When MDmn0 = 1 setting

Start trigger

detection signal

TCRmn

TDRmn

INTTMmn

f

MCK

(f

TCLK

)

TSmn (Write)

TEmn

TImn input

Rising edge

<1>

<3>

Edge detection

Note 1

<2>

Initial value

0000

0001

0000

m – 1 m 0000

0001

Note 1

m

<5>

<3>

<4>

Edge detection

Note 1. If a clock has been input to TImn (the trigger exists) when capturing starts, counting starts when a trigger is

detected, even if no edge is detected. Therefore, the first captured value (<4>) does not determine a pulse

interval (in the above figure, 0001 just indicates two clock cycles but does not determine the pulse interval)

and so the user can ignore it.

Caution In the first cycle operation of count clock after writing the TSmn bit, an error at a maximum of one

clock is generated since count start delays until count clock has been generated. When the

information on count start timing is necessary, an interrupt can be generated at count start by setting

MDmn0 = 1.

Loading...

Loading...